写在前面

本篇为学习 XILINX XC7Z020 开发板笔记。

这篇玩意我估计会超级长,打算 1-2 个月的时间来完成。其中包括了 FPGA、SDK、LINUX、PYNQ、以及硬件设计。

FPGA

首先要安装 VIVADO

https://china.xilinx.com/support/download.html

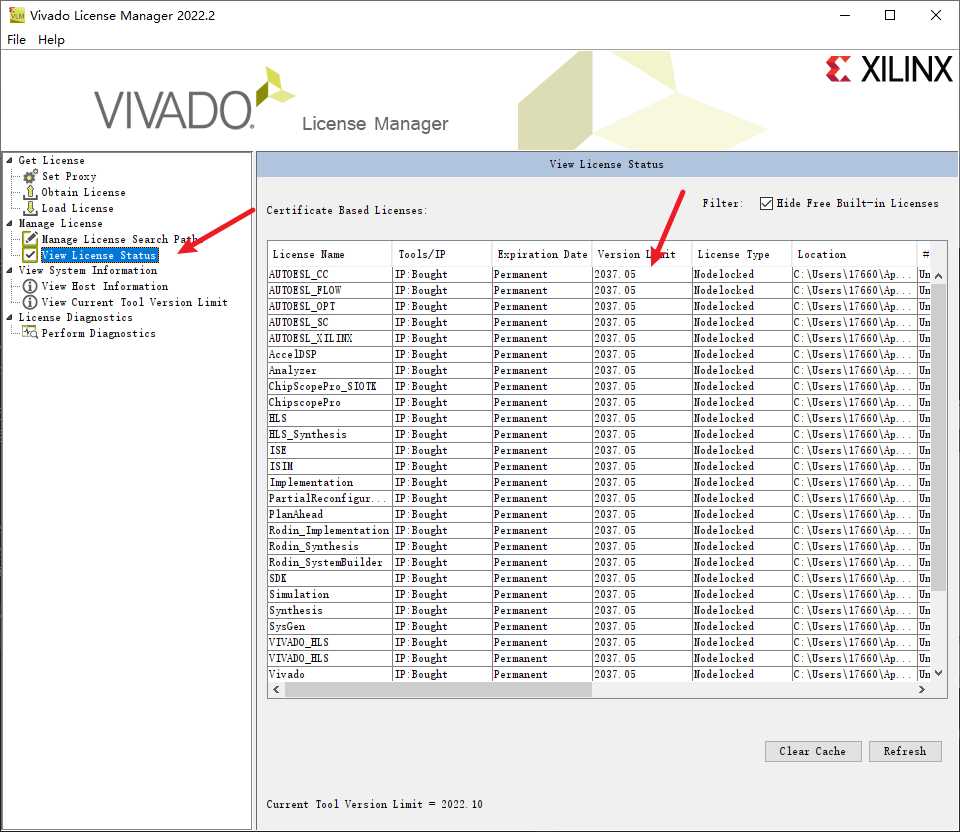

下载完成后安装,然后把破解 licence 放进去

看到时间就是完成了

一些基本的使用方法

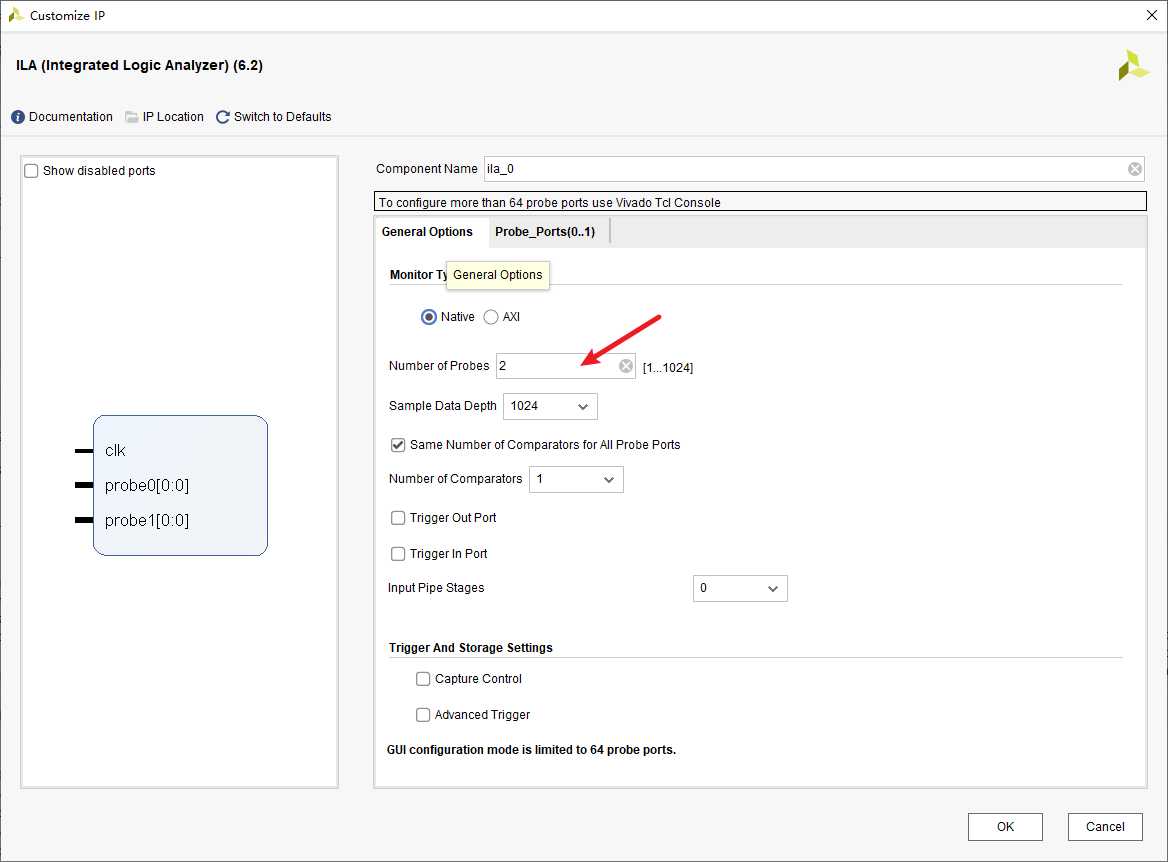

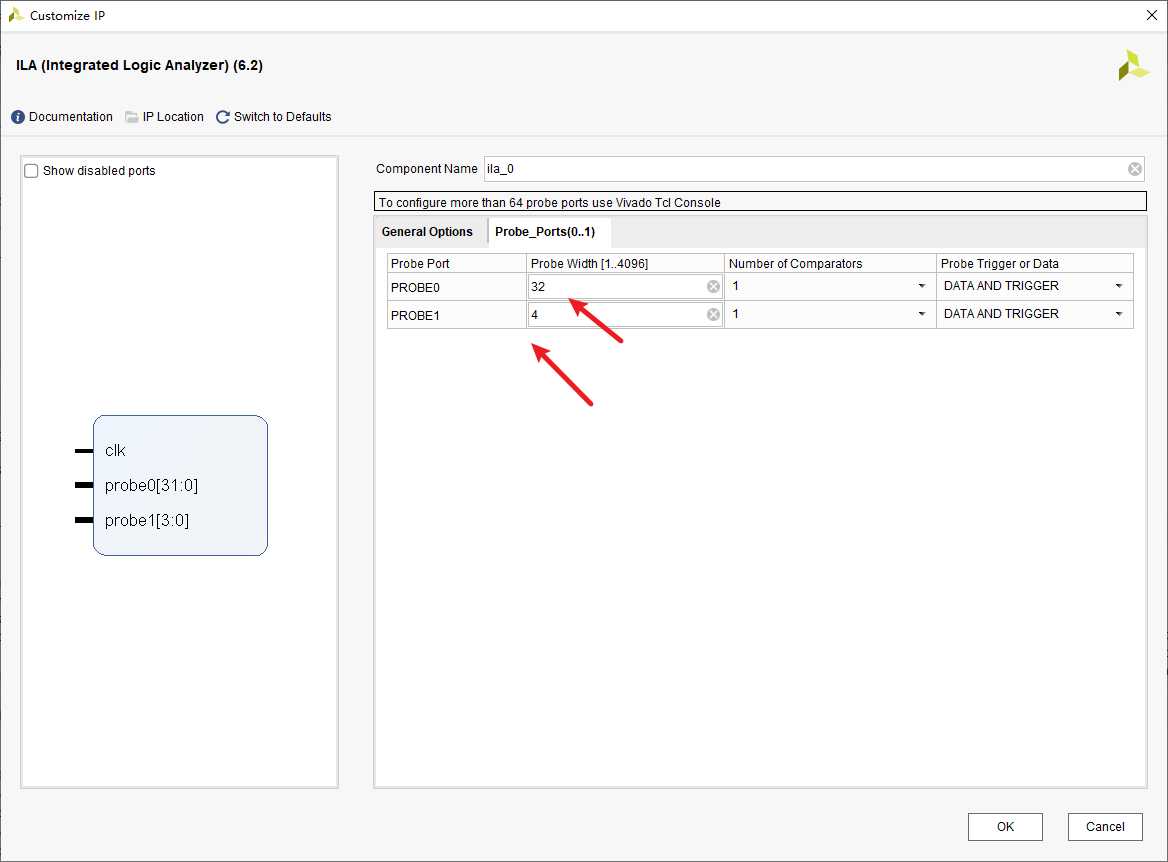

内嵌逻辑分析仪

然后就是一路 OK,Create,,

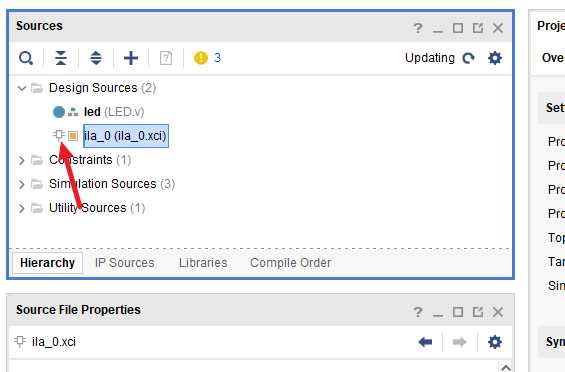

点这样一个小东西,展开 ILA 层级关系

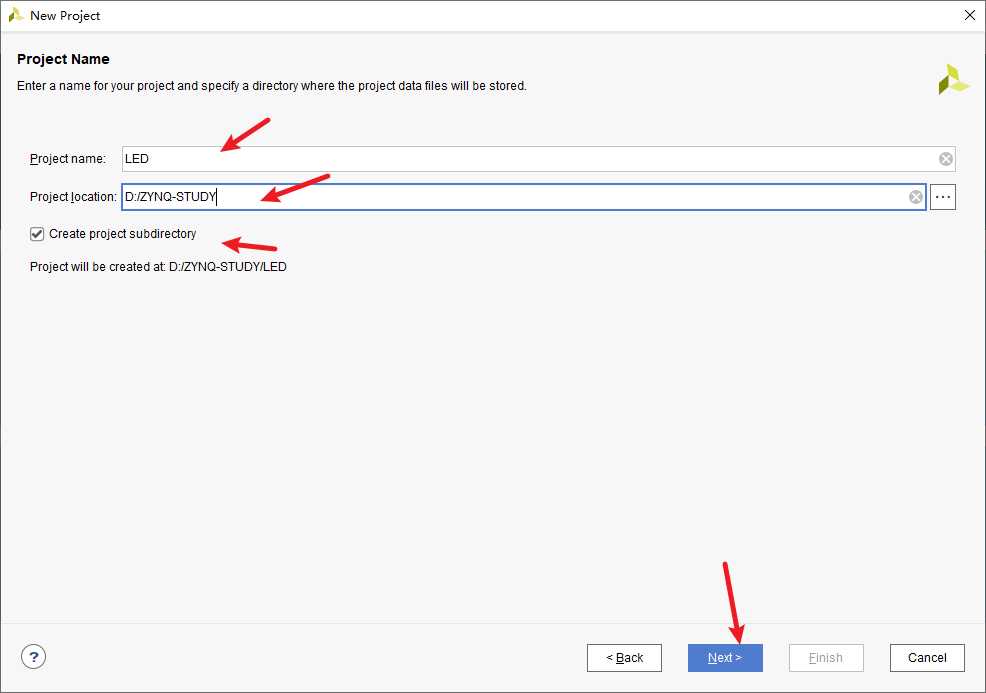

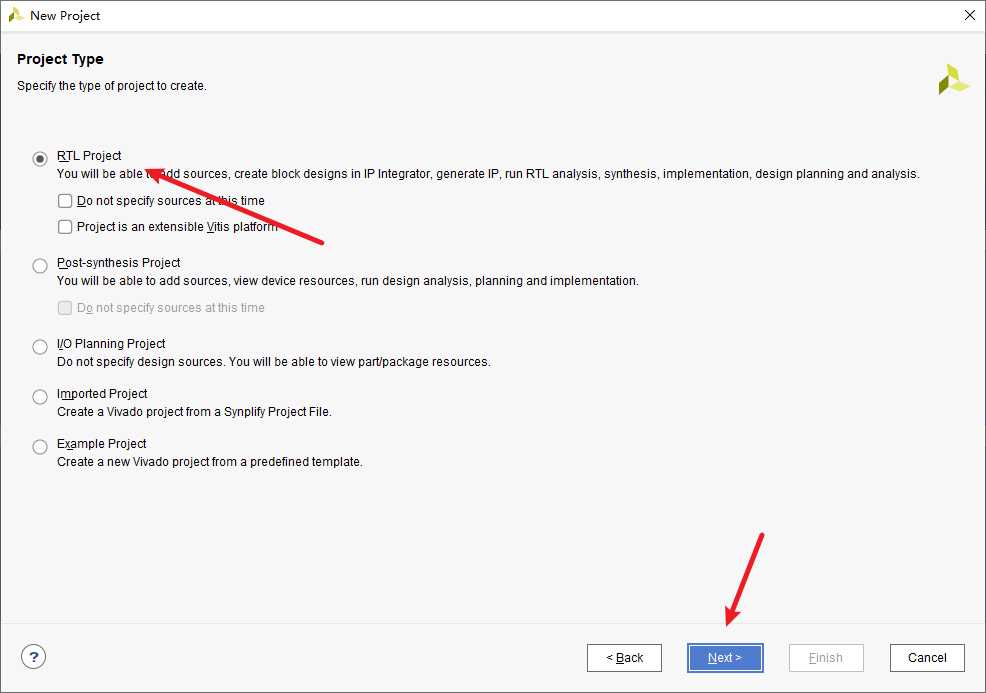

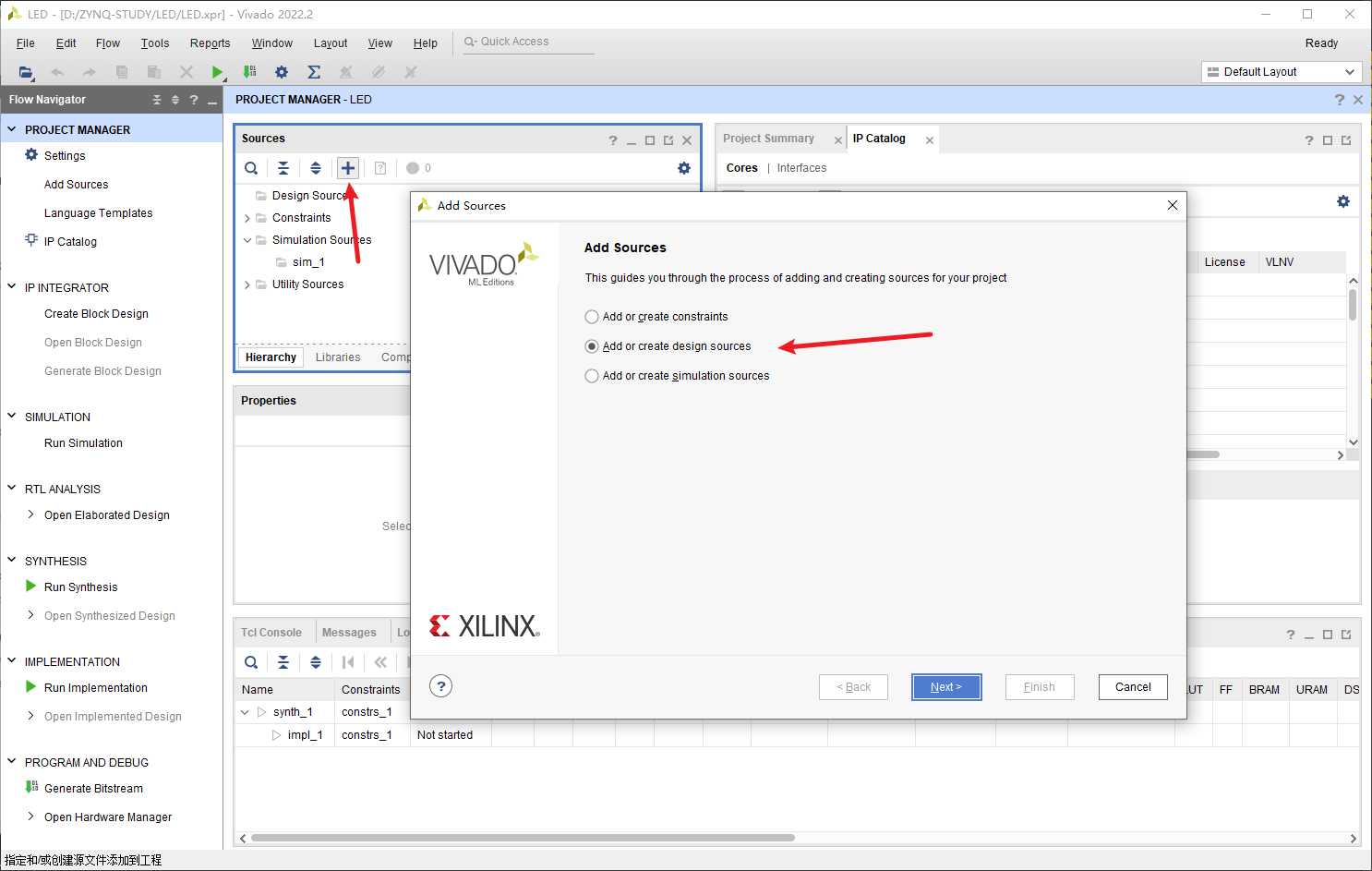

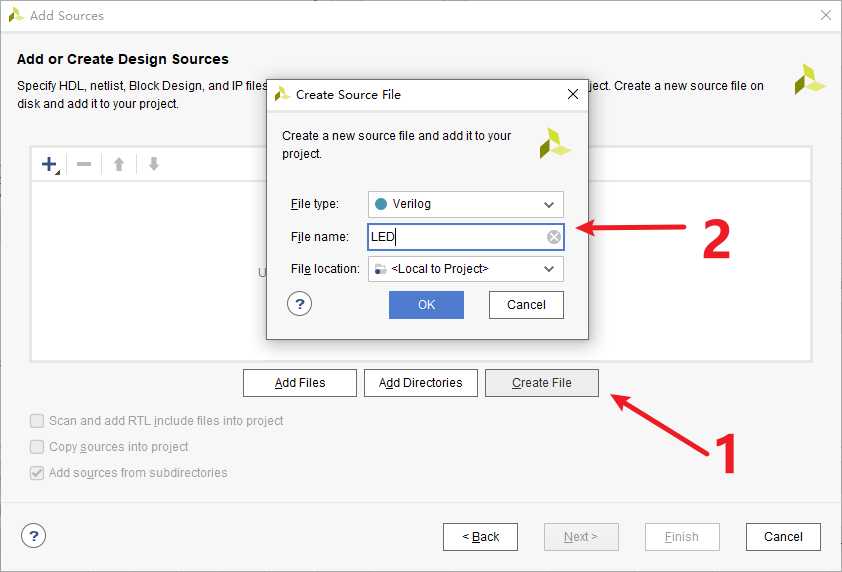

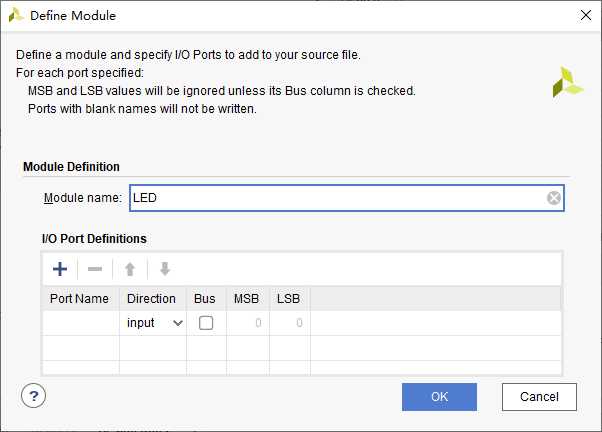

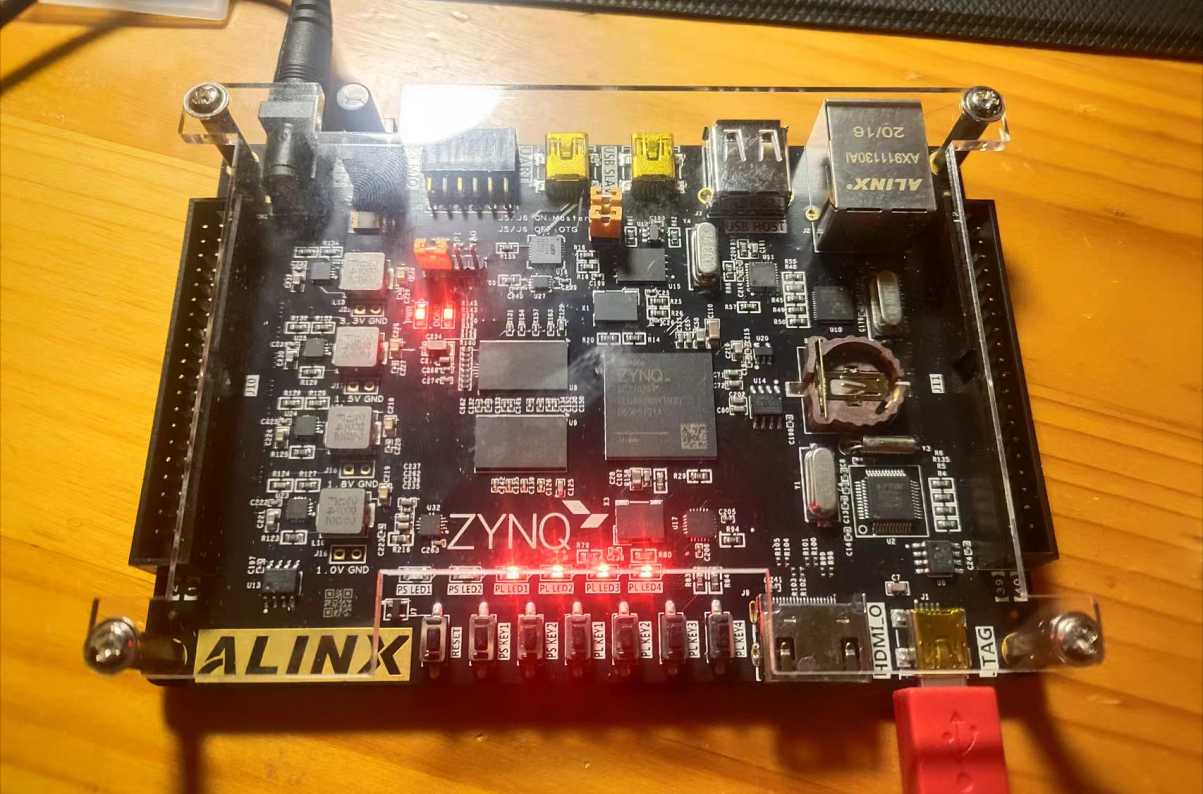

点灯

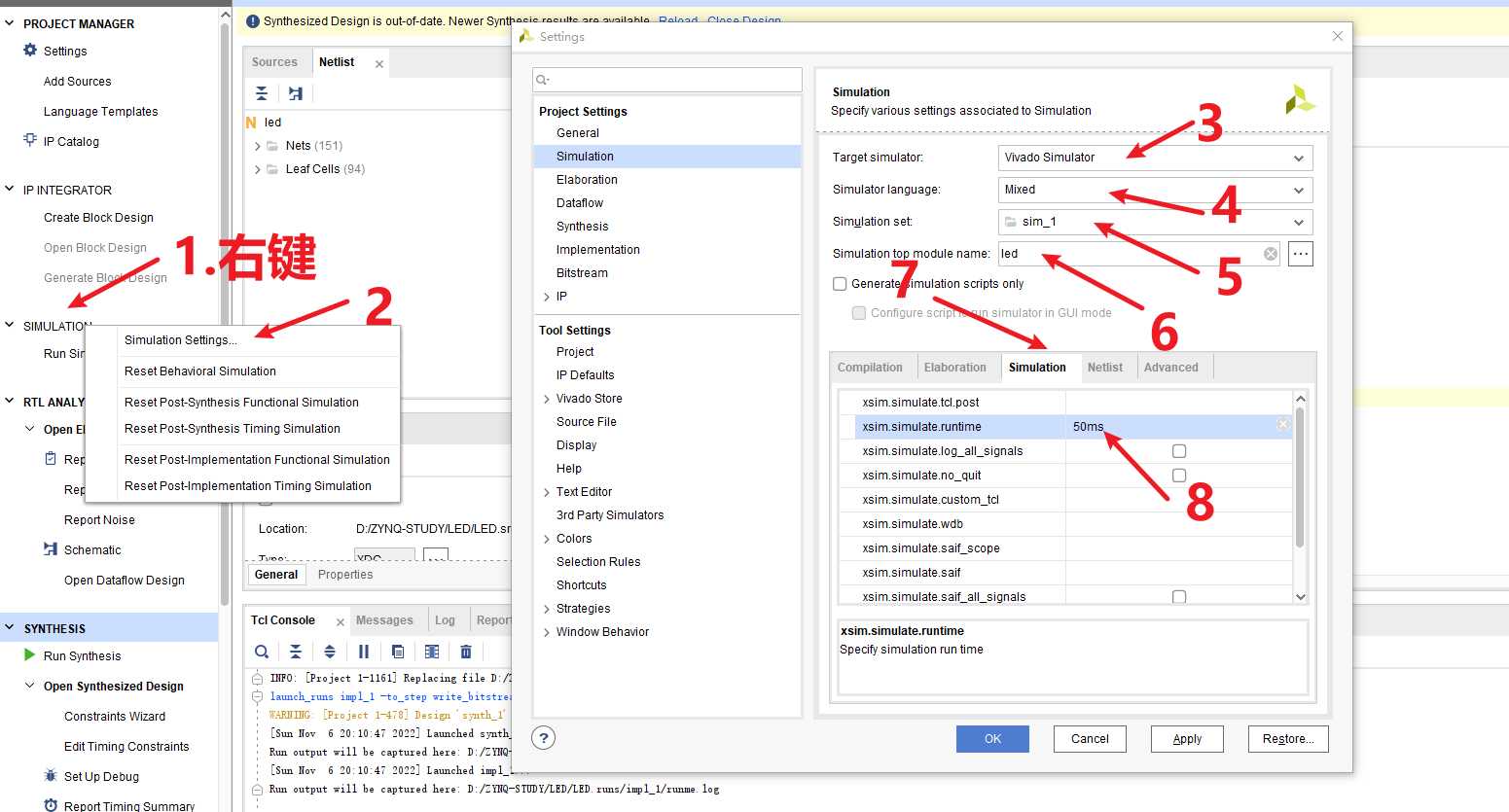

这里选择 Verilog,仿真选 Mixed ,Mixed 可以仿真 VHDL 和 Verilog HDL 两种语言。

添加约束这里不需要进行任何的操作

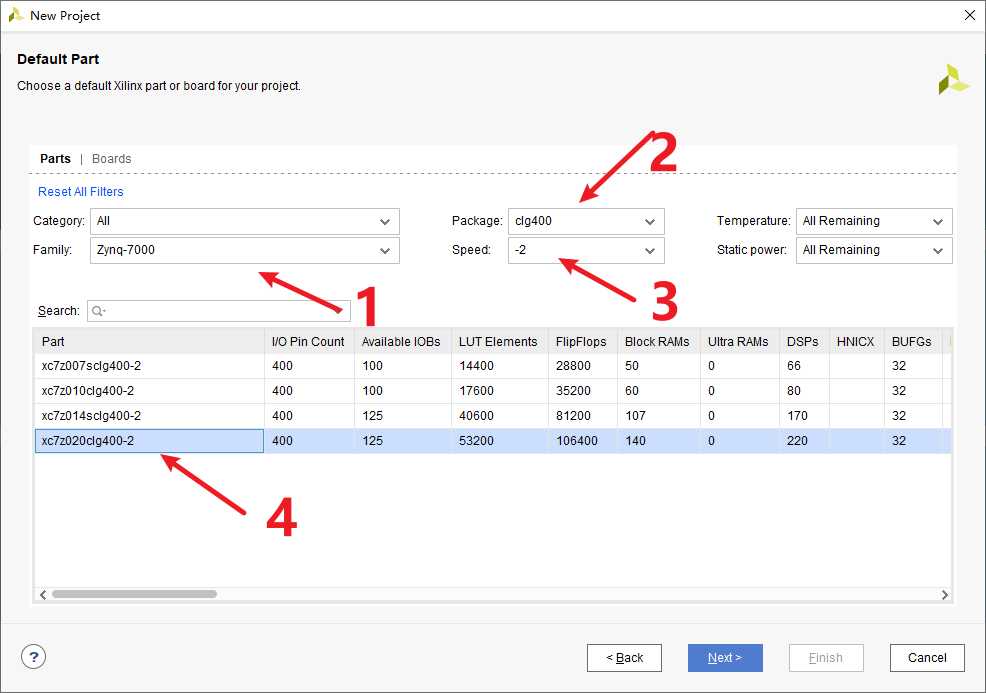

这个选型是针对 7Z020 芯片的,其他的需要根据手册自行选择

7Z010 要选择 -1 的速度;7Z020 要选择 -2 的速度;

Summary 有感叹号不重要,直接 Finish 就是了

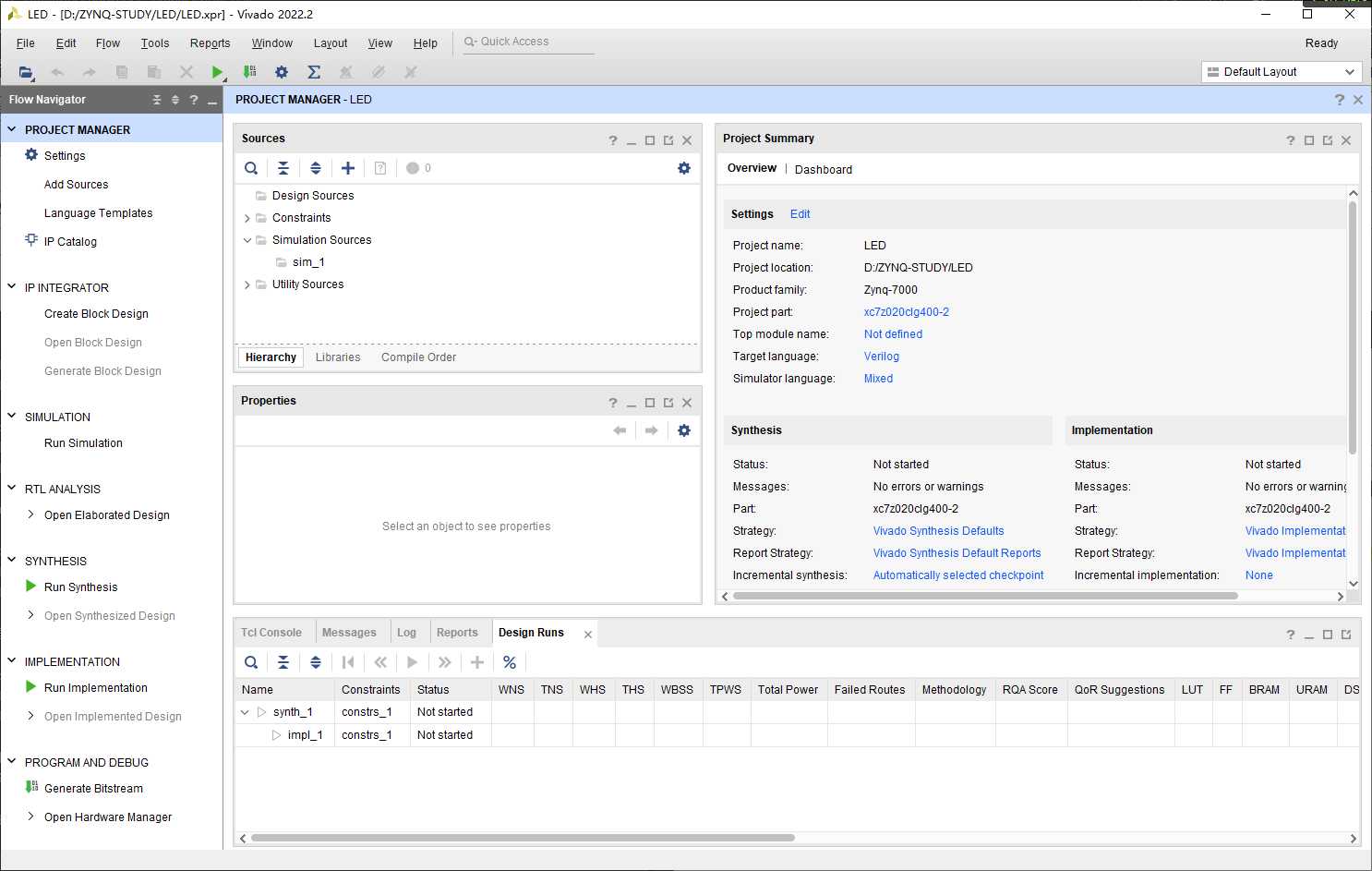

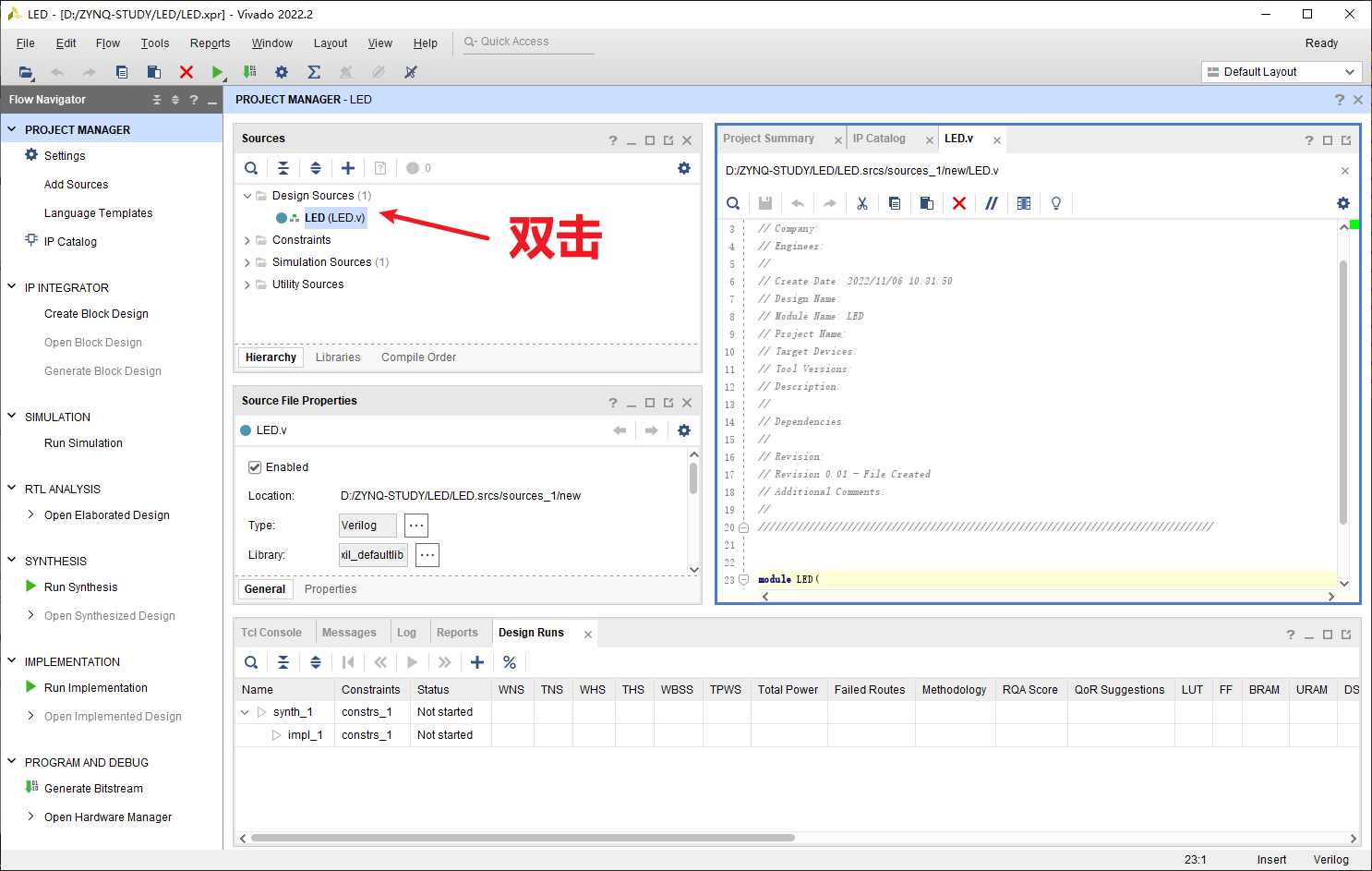

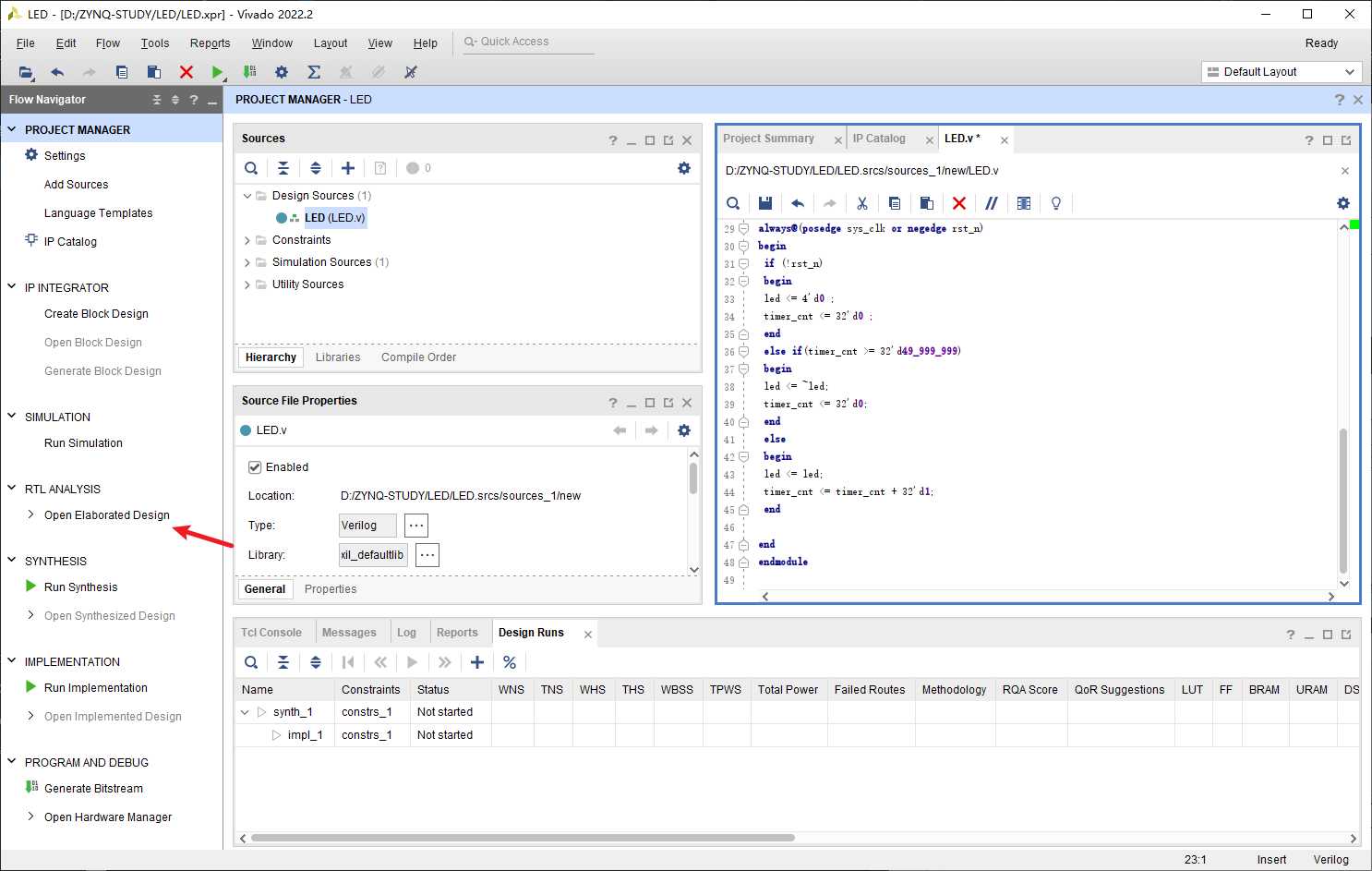

然后就能看到这样的界面

若有弹出提示窗口,则点击 OK

module led(

input sys_clk,

input rst_n,

output reg [3:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk or negedge rst_n)

begin

if (!rst_n)

begin

led <= 4'd0 ;

timer_cnt <= 32'd0 ;

end

else if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule

把例程代码复制黏贴到 module-endmodule 内(需要覆盖原有的

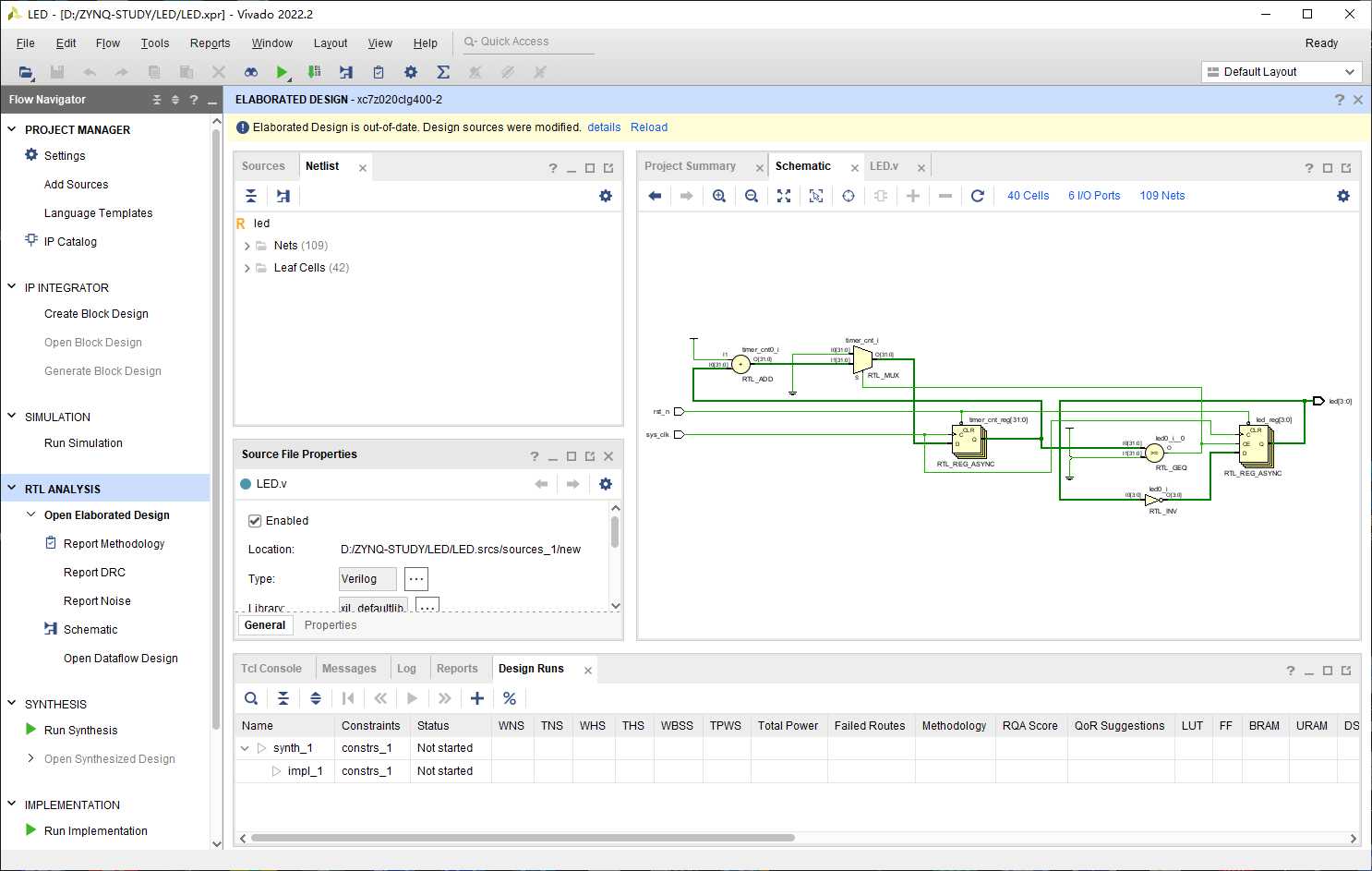

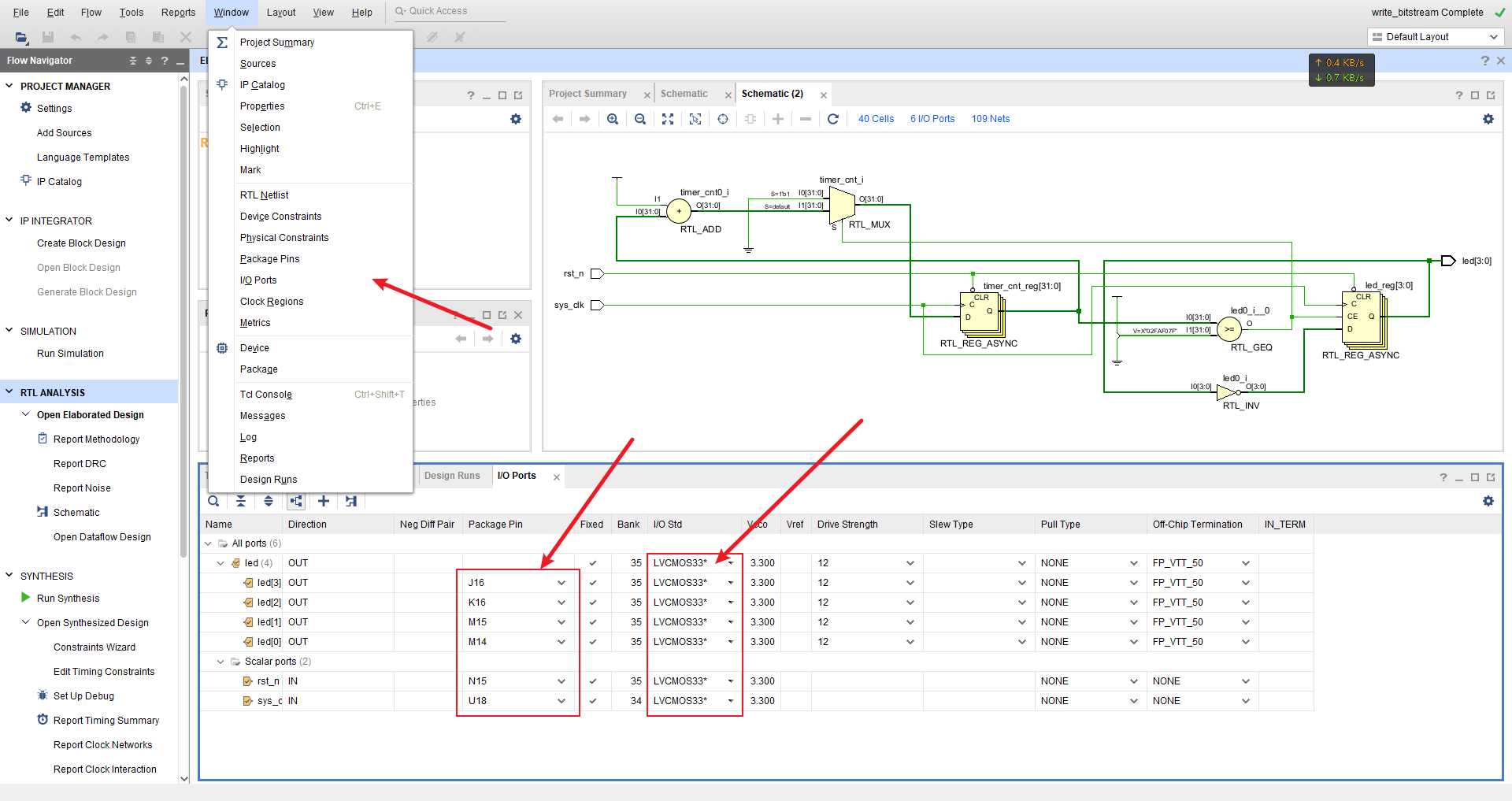

打开 IO 菜单,然后设置好端口和电压

普通 IO 口只需约束引脚号和电压,管脚约束如下:

set_property PACKAGE_PIN “引脚编号” [get_ports “端口名称”]

电平信号的约束如下:

set_property IOSTANDARD “电平标准” [get_ports “端口名称”]

这里需要注意文字的大小写,端口名称是数组的话用{ }刮起来,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样

电平标准中“LVCMOS33”后面的数字指 FPGA 的 BANK 电压,LED 所在 BANK 电压为 3.3伏,所以电平标准为“LVCMOS33”。Vivado 默认要求为所有 IO 分配正确的电平标准和管脚编号。

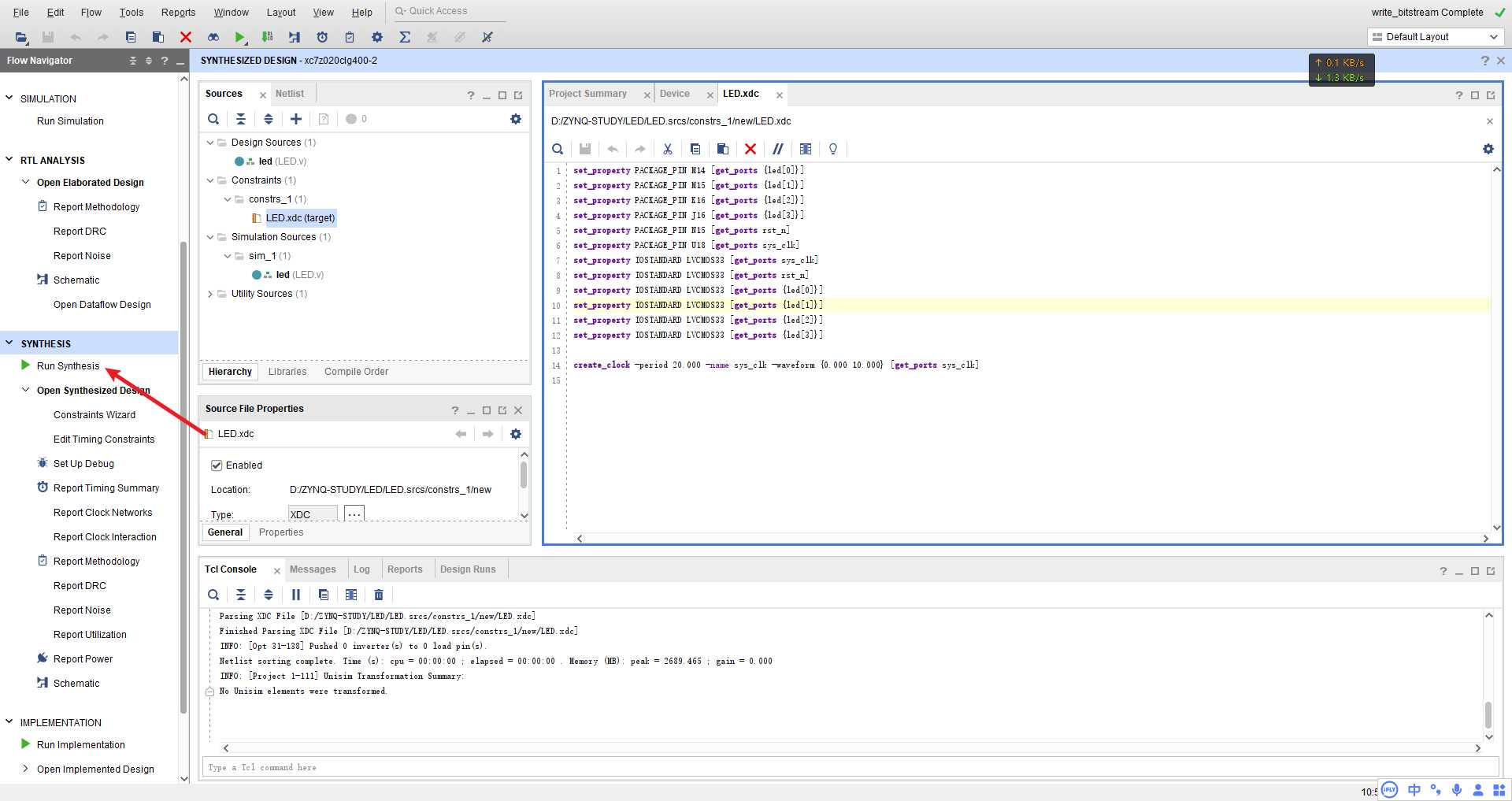

然后开始综合,这个步骤一路 OK即可,其中会有一步需要选择 CPU 核心数量,可以根据自己电脑性能进行选择

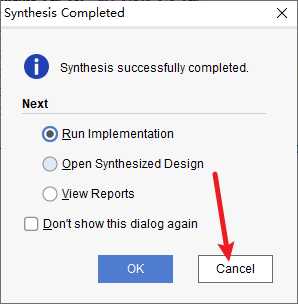

综合完成后我们需要添加约束条件,因此在这里点 Cancel

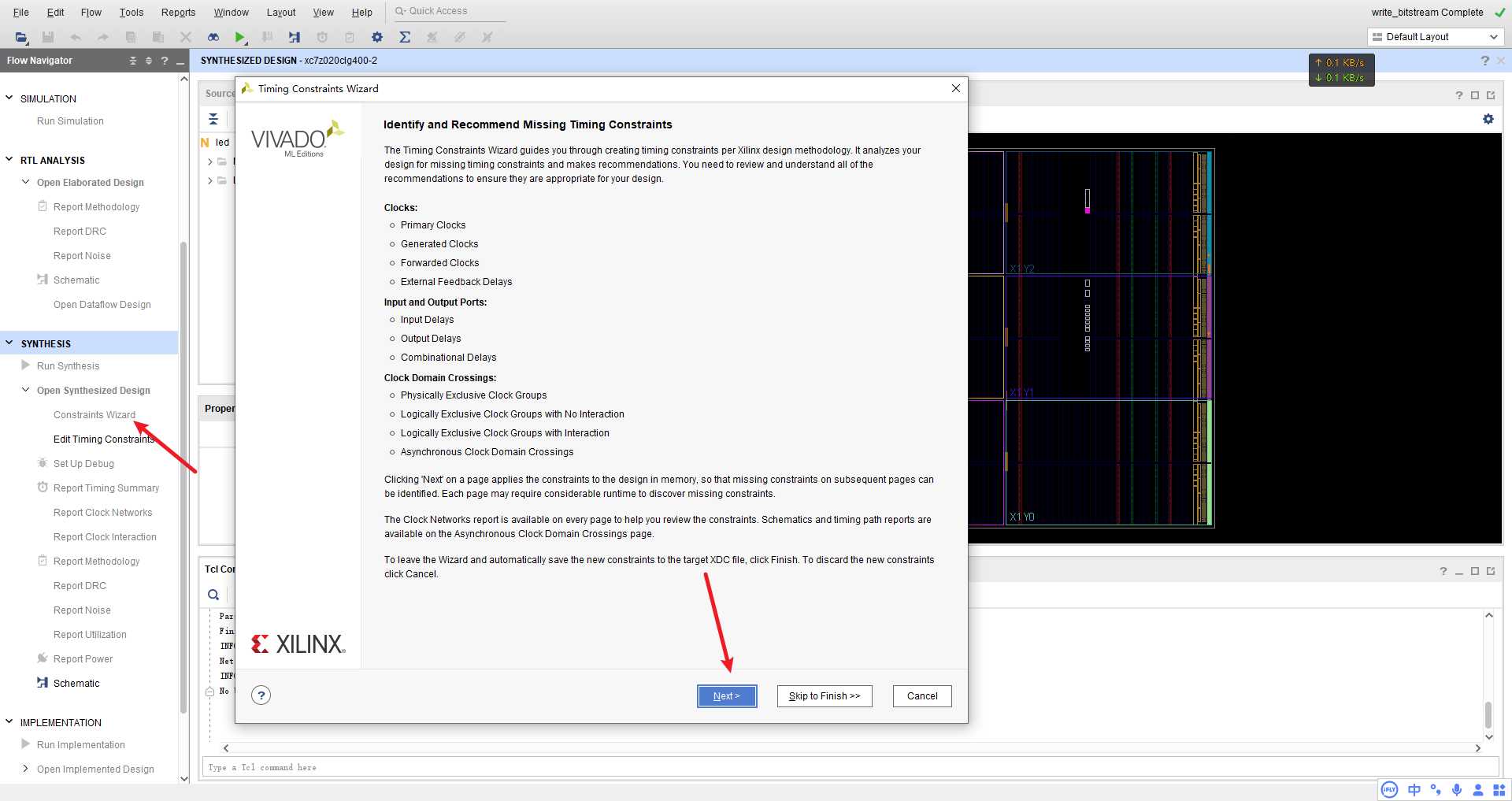

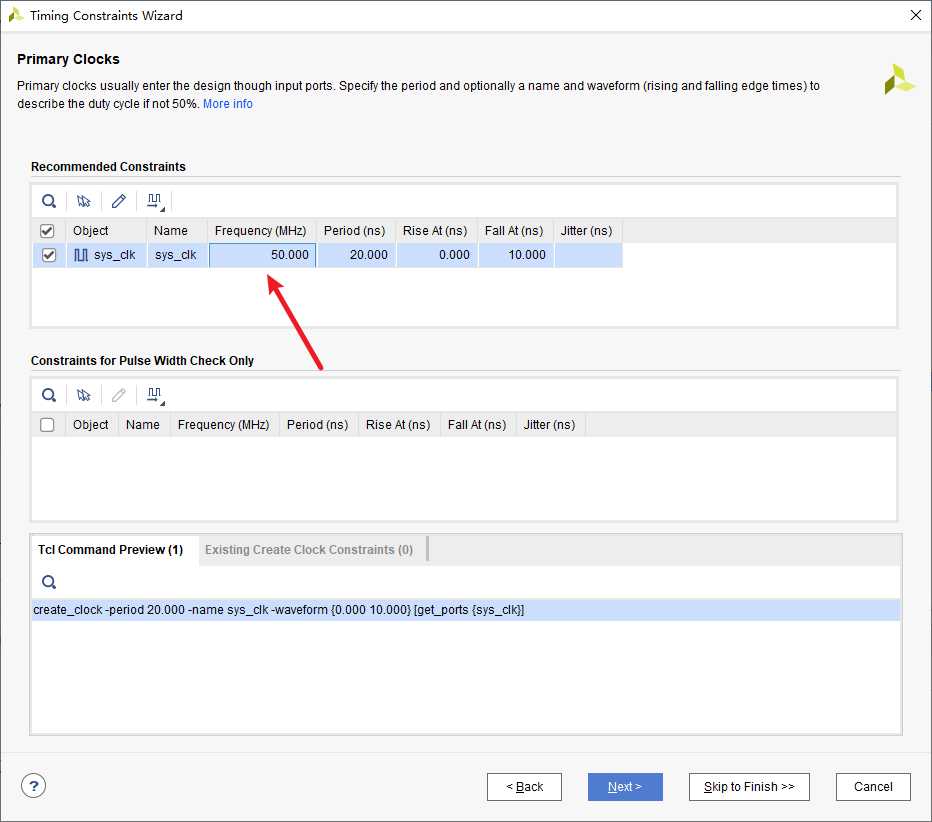

一个 FPGA 设计除了管脚分配以外,还有一个重要的约束,那就是时序约束,这里通过向导方式演示如果进行一个时序约束。

然后直接 Skip to Finish ,即可

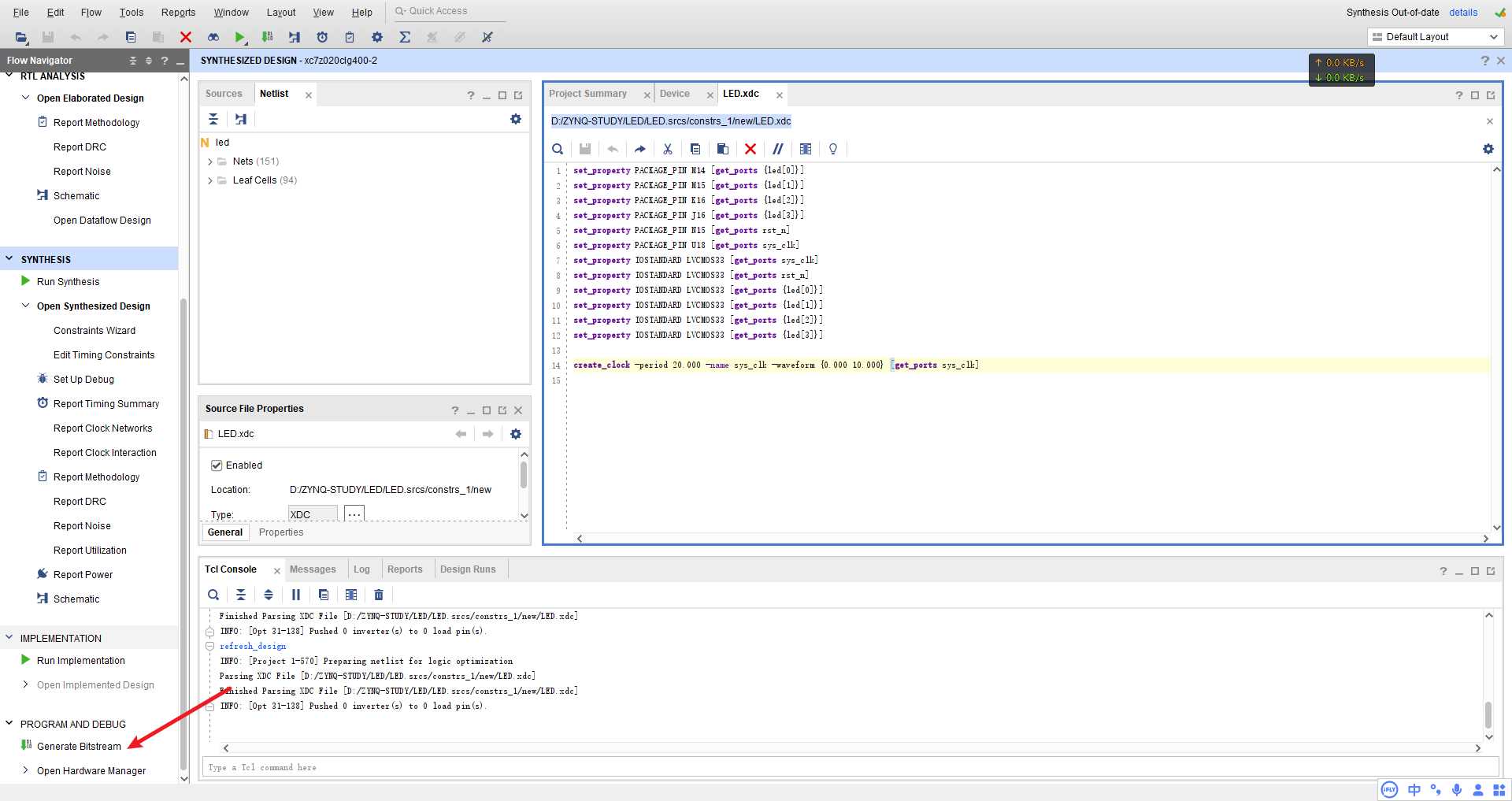

然后开始创建比特流,这一步同样需要选择 CPU 核心数,编译结束后需要进行仿真,同样的选择 Cancel

这一步是进行仿真设置

创建仿真文件

这里打错箭头了,要点 Finish,然后一路 OK

然后打开仿真文件,然后把代码复制进去

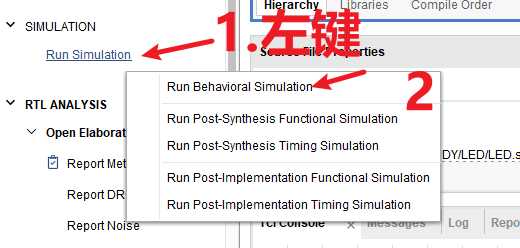

然后进行行为级仿真

WOC,VAVIDO 闪退了!

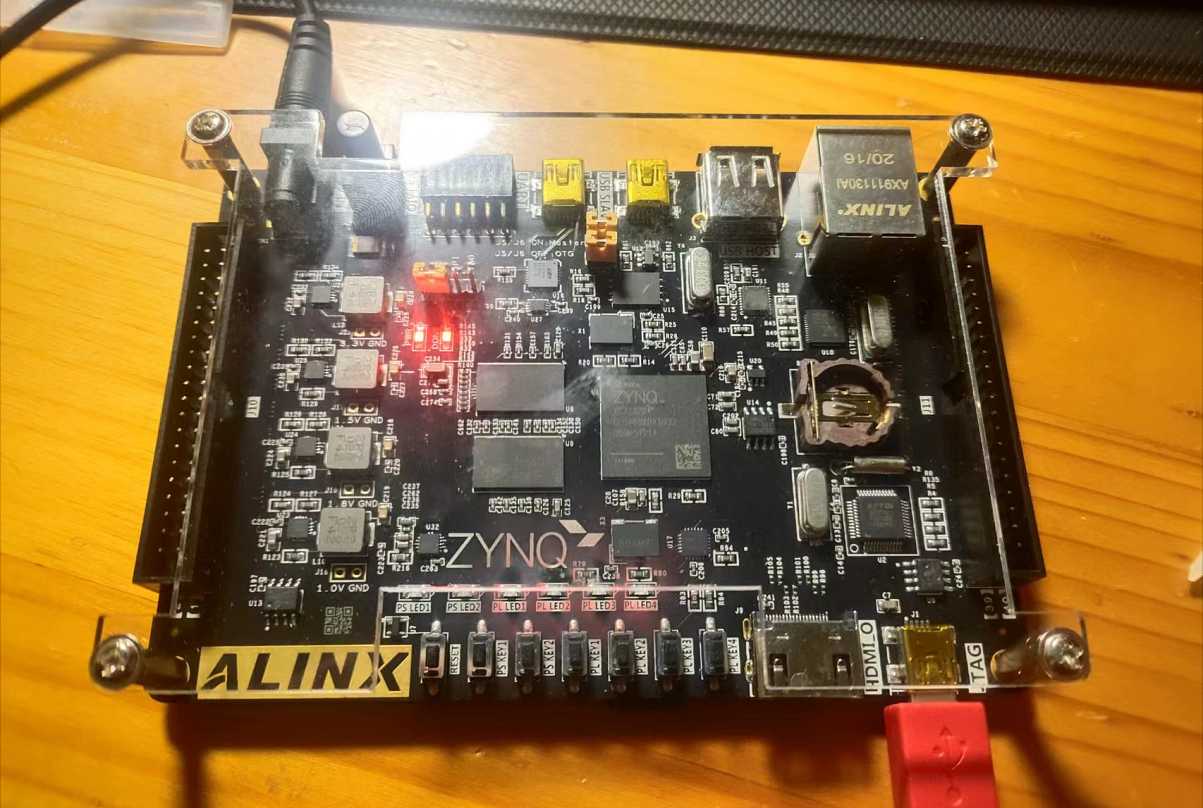

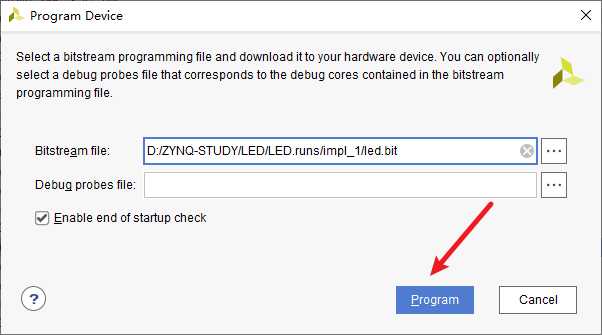

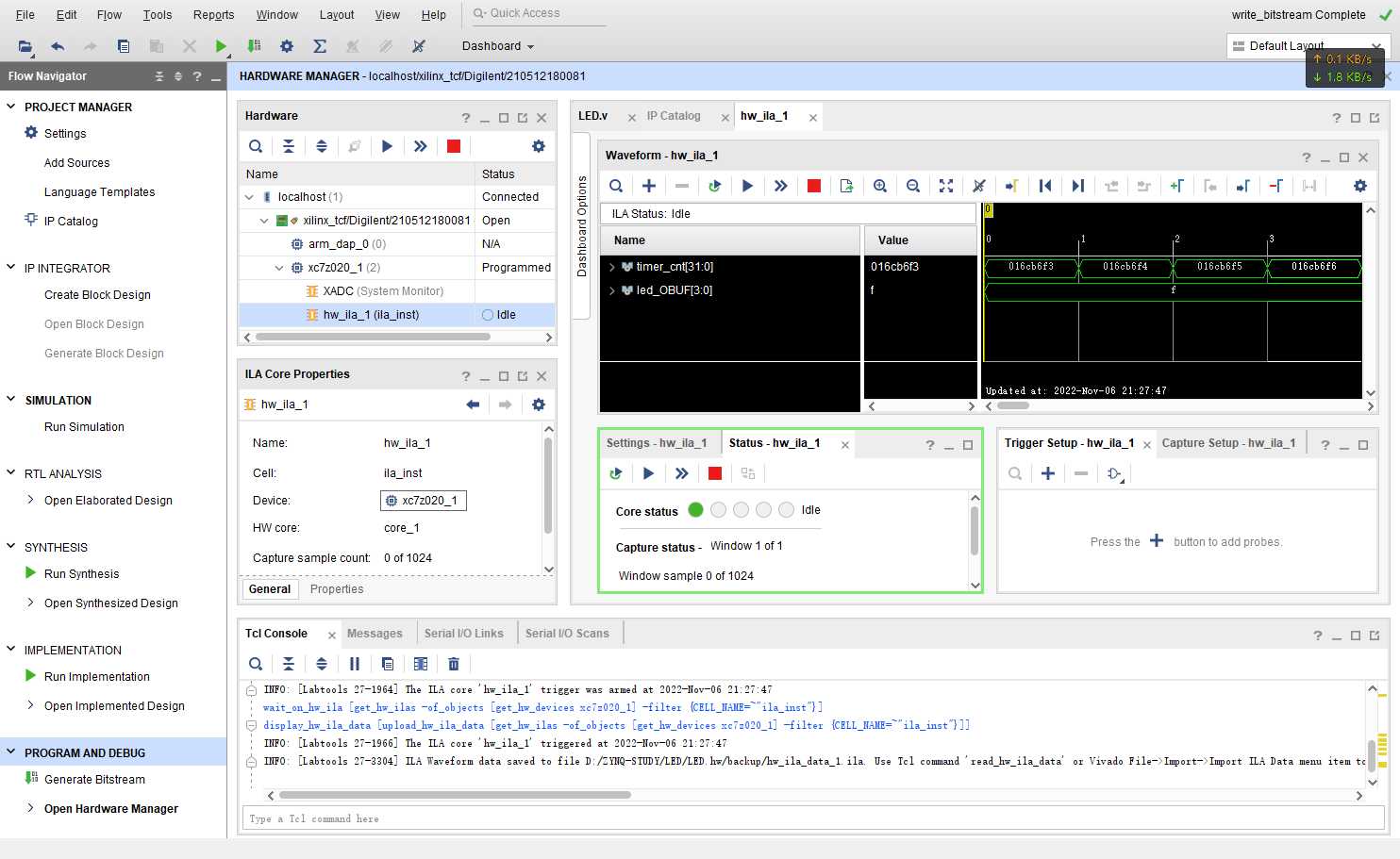

然后就是烧录了,这是需要连接板子的串口和电源,注意,先要把线全部接好,然后再上电

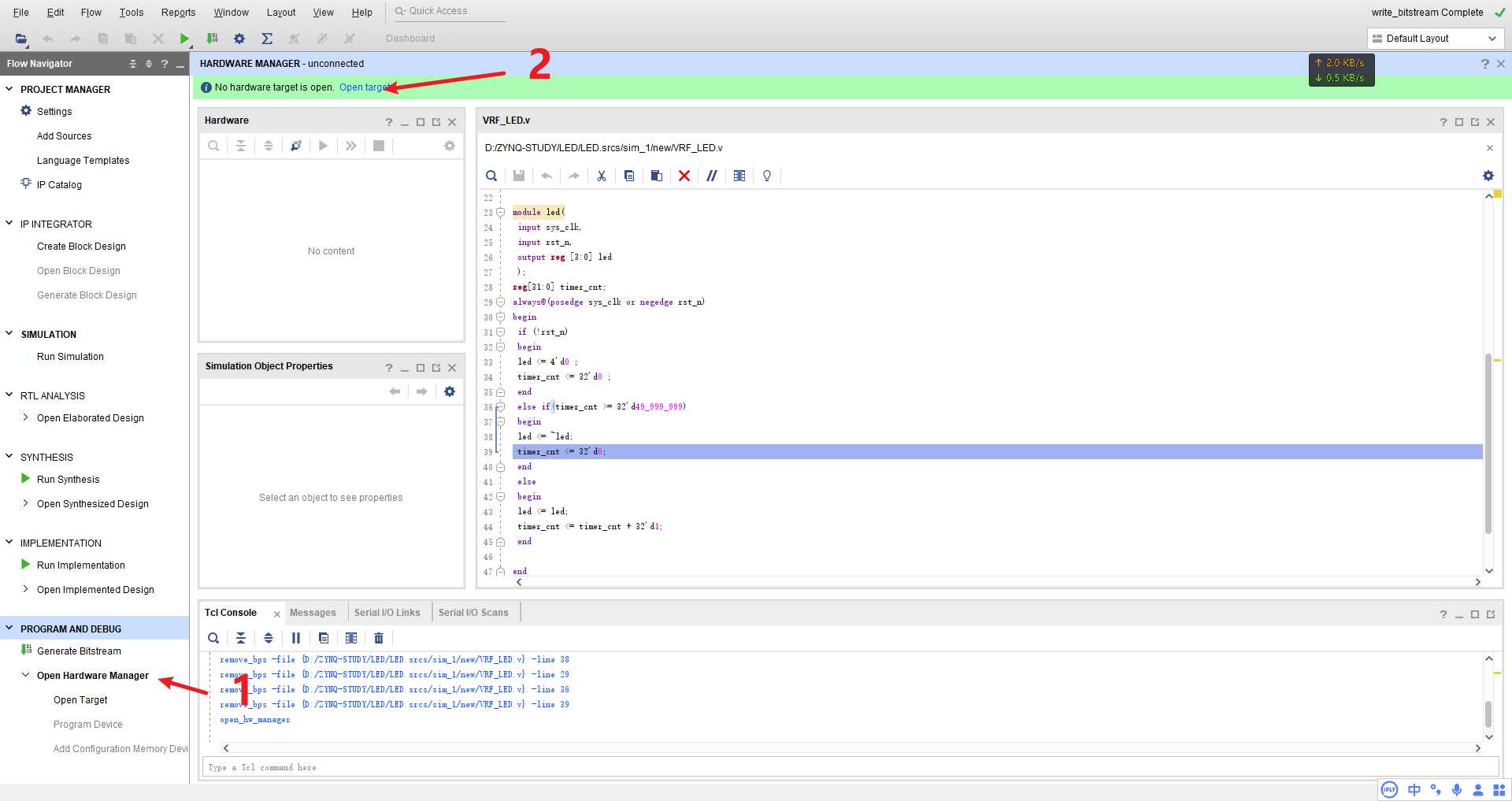

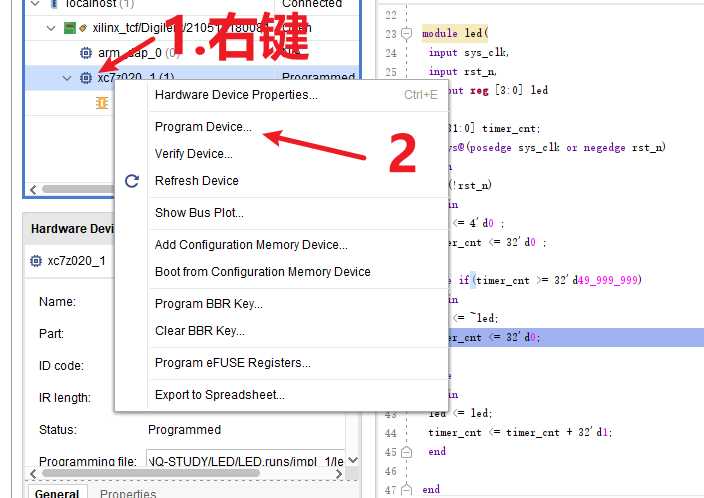

然后点 Auto Connect,然后如图

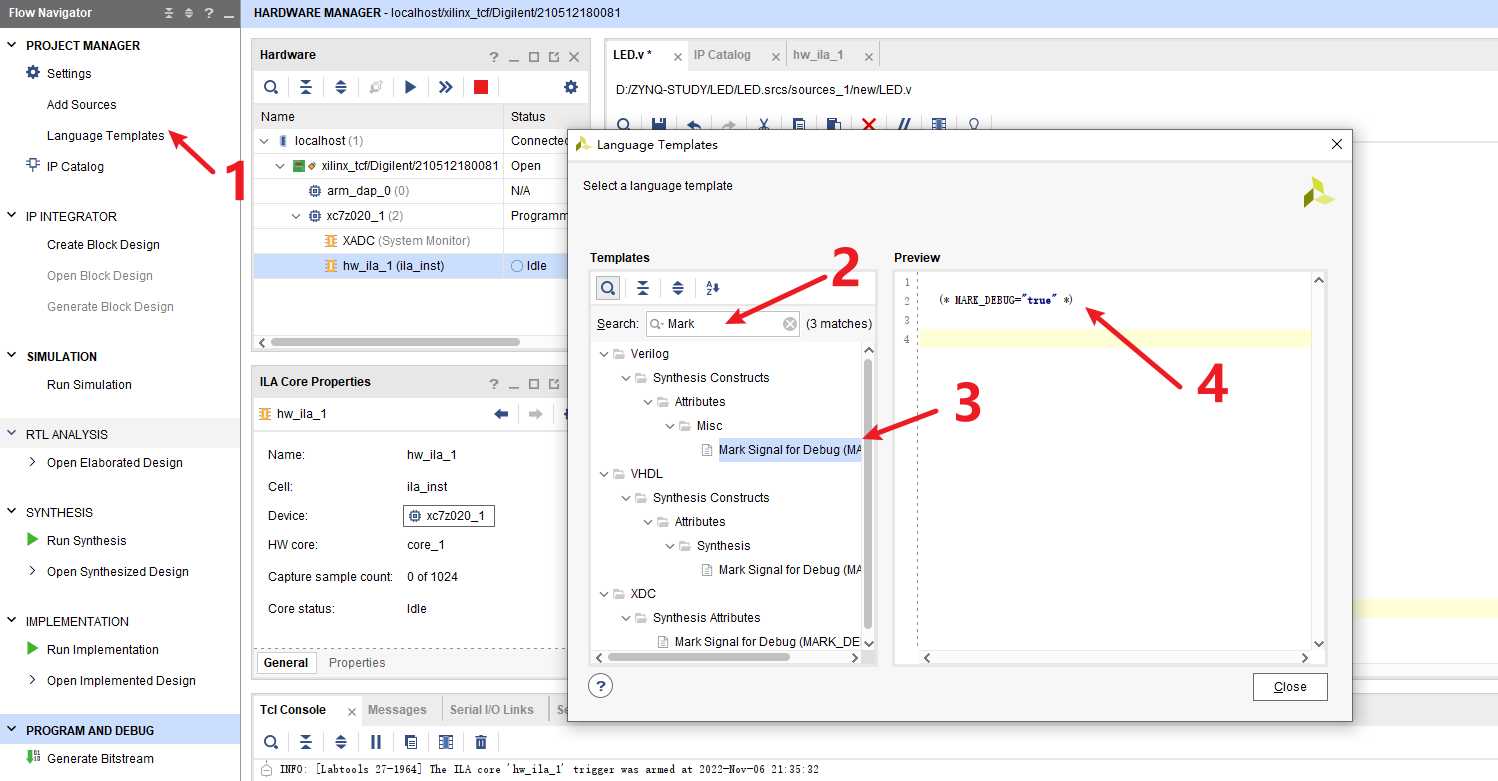

使用内嵌的逻辑分析仪,步骤如图

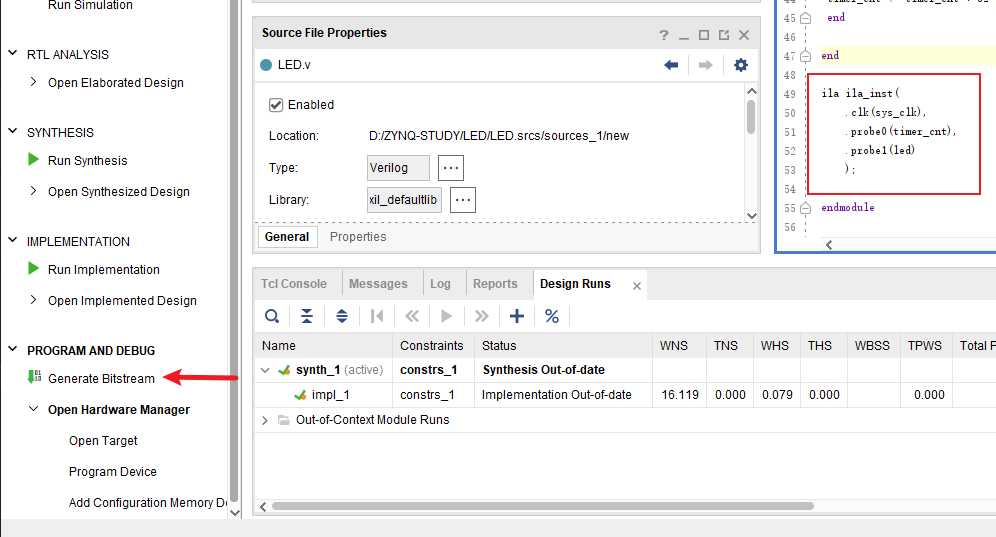

把代码复制进 LED.V 中,然后再一次生成比特文件

ila_0 ila_inst(

.clk(sys_clk),

.probe0(timer_cnt),

.probe1(led)

);

注意,这两处的名字要一样,不然无法创建比特流

然后重新烧录

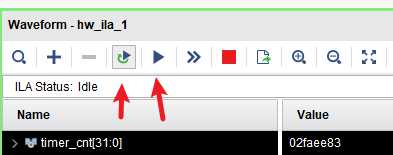

然后点一下 RUN 就能看到时序了

可以添加一下简单的触发条件

先点循环触发,再点 RUN,能进行一个循环的触发

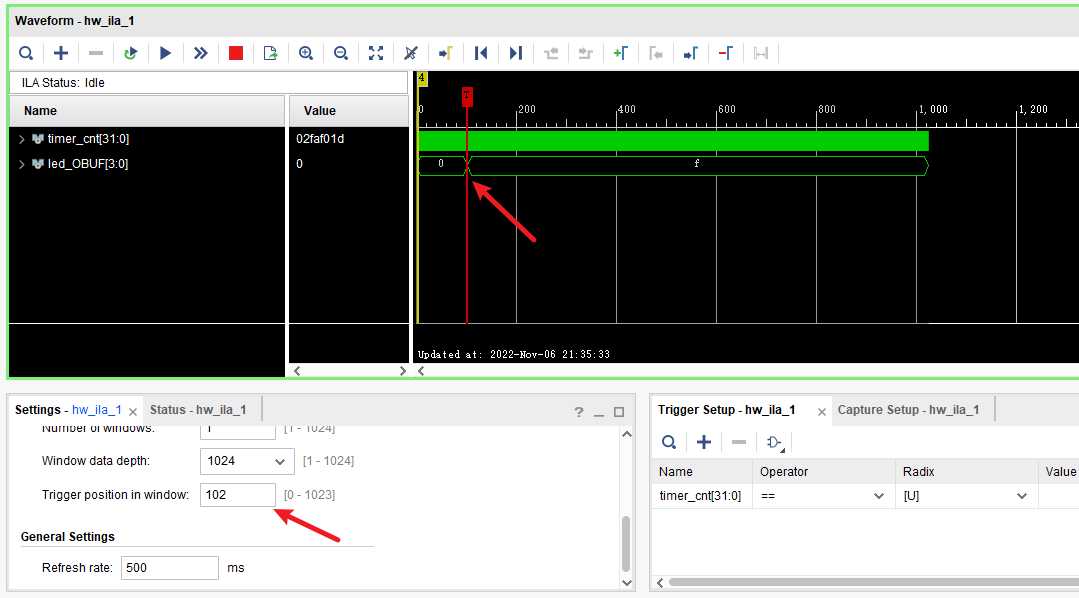

改变 Trigger Position in window,可以改变触发时序图的分布,增加被触发后的时序采样

Mark Debug 是在代码中添加综合属性,实现在线调试。两种逻辑分析的方法不一样,不能同时使用,因此需要把刚才的例化代码删掉

用 Language Templates 能快速查找想要的代码

然后把 (* MARK_DEBUG=”true” * ) 贴到需要 Debug 的端口前面

然后进行综合

是金钱的味道?

h

催更

我把开发板忘记在家里了,等我做完毕设就回家拿,sorry~~