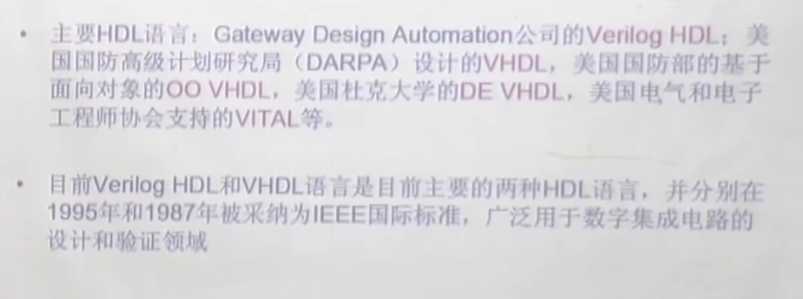

概述

目前美国的设计公司用的主要是Verilog HDL,欧洲的设计公司主要用VHDL

Verilog HDL 的语法非常宽松,在大型电路设计的时候容易出现问题,但对于初学者来说相对容易上手

VHDL 的语法非常严谨,不太好上手

从 2002 年开始,出现了两种语言联合编译

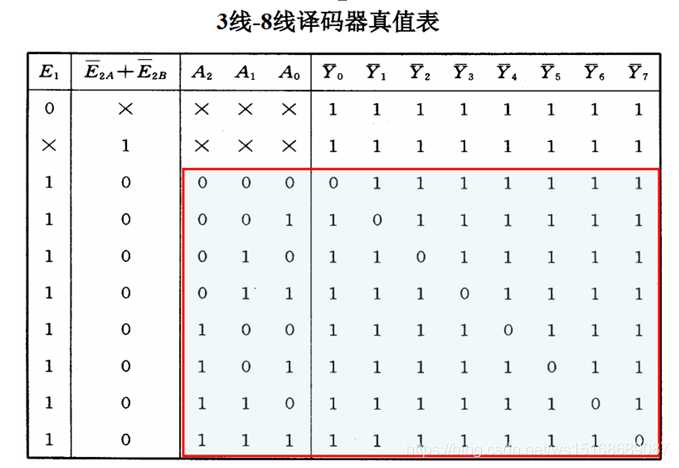

3-8 译码器

这是 3-8 译码器的真值表

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY decoder3to8 IS

PORT(A:IN STD_LOGIC_VECTOR(2 DOWNtO 0);

ST,STA,STB:IN STD_LOGIC;

Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY decoder3to8;

ARCHITECTURE 3to8 OF decoder3to8

BEGIN

PROCESS(A)

BEGIN

IF ST="1" AND STA="0" AND STB="0" THEN

BEGIN

CASE(A) IS

WHEN "000" => Y <= "11111110";

WHEN "001" => Y <= "11111101";

WHEN "010" => Y <= "11111011";

WHEN "011" => Y <= "11110111";

WHEN "100" => Y <= "11101111";

WHEN "101" => Y <= "11011111";

WHEN "110" => Y <= "10111111";

WHEN OTHERS => Y <= "01111111";

END CASE;

ELSE Y <= "11111111";

END IF;

END PROCESS;

END 3to8;

4 选 1 选择器

试分别用IF_THEN语句、WHEN_ELSE 和CASE语句的表达方式写出4选1多路选择器的VHDL程序,选通控制端有4个输入:S0、S1、S2、S3。当且仅当S0=0,时:Y=A;S1=0时:Y=B;S2=0时:Y=C; S3=0时:Y=D。

LIBRERY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT( S0,S1,S2,S3 :IN STD_LOGIC;

A,B,C,D : IN STD_LOGIC;

Y: OUT: STD_LOGIC );

END ENTITY mux41;

ARCHITECTURE one OF mux41 IS

SIGNAL S : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S=S3&S2&S1&S0 ;

PROCESS(S0,S1,S2,S3) BEGIN

IF (S= "1110") THEN Y<=A ;

ELSIF (S= "1101" ) THEN Y<=B;

ELSIF (S= "1011" ) THEN Y<=C;

ELSIF (S= "0111" ) THEN Y<=D ;

END IF ;

END PROCESS;

END one;

试用WITH- -SELECT语句写出4选1多路选择器的VHDL程序,选通控制端有4个输入:S0、S1、S2、S3。当且仅当S0=0,时:Y=A;S1=0时:Y=B;S2=0时:Y=C; S3=0时:Y=D。

LIBRERY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT( S0,S1,S2,S3 :IN STD_LOGIC;

A,B,C,D : IN STD_LOGIC;

Y: OUT: STD_LOGIC );

END ENTITY mux41;

ARCHITECTURE one OF mux41 IS

SIGNAL S : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S=S3&S2&S1&S0 ;

WITH S SELECT

Y<=A WHEN "1110" ;

B WHEN "1101" ;

C WHEN "1011" ;

D WHEN "0111" ;

NULL WHEN OTHERS;

END one;

试用IWHEN_ELSE 语句写出4选1多路选择器的VHDL程序,选通控制端有4个输入:S0、S1、S2、S3。当且仅当S0=0,时:Y=A;S1=0时:Y=B;S2=0时:Y=C; S3=0时:Y=D。

LIBRERY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT( S0,S1,S2,S3 :IN STD_LOGIC;

A,B,C,D : IN STD_LOGIC;

Y: OUT: STD_LOGIC );

END ENTITY mux41;

ARCHITECTURE one OF mux41 IS

SIGNAL S : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S=S3&S2&S1&S0 ;

Y<=A WHEN S="1110" ELSE ;

B WHEN S="1101" ELSE ;

C WHEN S="1011" ELSE;

D WHEN S= "0111" ELSE;

NULL ;

END one;

试用CASE语句写出4选1多路选择器的VHDL程序,选通控制端有4个输入:S0、S1、S2、S3。当且仅当S0=0,时:Y=A;S1=0时:Y=B;S2=0时:Y=C; S3=0时:Y=D。

LIBRERY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT( S0,S1,S2,S3 :IN STD_LOGIC;

A,B,C,D : IN STD_LOGIC;

Y: OUT: STD_LOGIC );

END ENTITY mux41;

ARCHITECTURE one OF mux41 IS

SIGNAL S : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

S=S3&S2&S1&S0 ;

PROCESS(S0,S1,S2,S3) BEGIN

CASE (S) IS

WHEN "1110" => Y<=A ;

WHEN "1101" => Y<=B;

WHEN "1011" => Y<=C;

WHEN "0111" => Y<=D ;

WHEN OTHERS =>NULL ;

END CASE;

END PROCESS;

END one;

设计一个求补码的VHDL程序

输入数据是一个有符号的8位二进制数

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY buma IS

PORT(a:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END buma;

ARCHITECTURE arc OF buma IS

SIGNAL tmp:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(a)

BEGIN

IF a(7)='0' THEN

y<=a;

ELSE

tmp(7)<='1';

FOR i IN 0 TO 6 LOOP

tmp(i)<=NOT a(i);

y<=tmp+1;

END LOOP;

END IF;

END PROCESS;

END arc;

设计一个4 位乘法器

为此首先设计一个加法器,用例化语句调用这个加法器,用移位相加的方式完成乘法

并以此项设计为基础,使用GENERIC参数传递的功能设计一个16位乘法器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY MULT4B IS

GENERIC( S: INTEGER:=4); --定义参数S为整数类型,且等于4

PORT( R: OUT STD_LOGIC_VECTOR(2*S-1 DOWNTO 0);

A,B: IN STD_LOGIC_VECTOR(S-1 DOWNTO 0));

END ENTITY MULT4B;

ARCHITECTURE ONE OF MULT4B IS COMPONENT addern IS

PORT(a,b: IN STD_LOGIC_VECTOR; result: out STD_LOGIC_VECTOR);

END COMPONENT;

SIGNAL A0: STD_LOGIC_VECTOR(2*S-1 DOWNTO 0);

SIGNAL RR3,RR2,RR1,RR0,ZZ1,ZZ0: STD_LOGIC_VECTOR(2*S-1 DOWNTO 0);

BEGIN

A0<=CONV_STD_LOGIC_VECTOR(0,S) & A;

PROCESS(A,B)

BEGIN

IF(B(0)='1')THEN RR0<=TO_STDLOGICVECTOR(TO_BITVECTOR(A0) SLL 0);

ELSE RR0<=(OTHERS=>'0');

END IF;

IF(B(1)='1')THEN RR1<=TO_STDLOGICVECTOR(TO_BITVECTOR(A0) SLL 1);

ELSE RR1<=(OTHERS=>'0');

END IF;

IF(B(2)='1')THEN RR2<=TO_STDLOGICVECTOR(TO_BITVECTOR(A0) SLL 2);

ELSE RR2<=(OTHERS=>'0');

END IF;

IF(B(3)='1')THEN RR3<=TO_STDLOGICVECTOR(TO_BITVECTOR(A0) SLL 3);

ELSE RR3<=(OTHERS=>'0');

END IF;

END PROCESS;

u0: addern PORT MAP(a=>RR0,b=>RR1,result=>ZZ0);

u1: addern PORT MAP(a=>ZZ0,b=>RR2,result=>ZZ1);

u2: addern PORT MAP(a=>ZZ1,b=>RR3,result=>R);

END ARCHITECTURE ONE;

D类触发器

写出具有上升沿触发的D触发器的VHDL语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF1 IS

PORT(CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF DFF1 IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK='1'

THEN Q1 <= D;

END IF;

END PROCESS;

Q <= Q1;

END bhv;

写出具有异步复位和时钟使能的上升沿触发的D触发器的VHDL语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF2 IS

PORT(CLK,RST,EN,D:IN STD_LOGIC;

Q:OUT SYD_LOGIC);

END;

ARCHITECTURE bhv OF DFF2 IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS(CLK,Q1,RST,EN)

BEGIN

IF RST='1' THEN Q<='0';

ELSIF CLK'EVENT AND CLK='1'THEN

IF EN='1' THEN Q1<=D;

END IF;

END PROCESS;

Q<=Q1;

END bhv;

写出具有同步复位控制的上升沿触发的D触发器的VHDL语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF3 IS

PORT(CLK,RST,D:IN ATD_LOGIC;

Q:OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF DFF3 IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS (CLK,Q1,RST)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF RST='1' THEN Q1<='0';

ELSE Q1<=D;

END IF;

END IF;

END PROCESS;

Q<=Q1;

END bhv;

锁存器

写出基本锁存器的VHDL语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENITIY LTCH2 IS

PORT (CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF LTCH2 IS

BEGIN

PROCESS (CLK,D)

BEGIN

IF CLK='1' THEN Q<=D;

END IF;

END PROCESS;

END bhv;

写出含清零控制的锁存器的VHDL语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LTCH3 IS

PORT (CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF LTCH3 IS

BEGIN

PROCESS (CLK,D,RST)

BEGIN

IF RST='1' THEN Q<='0';

ELSIF CLK='1' THEN Q<=D;

END IF;

END PROCESS;

END bhv;

加法器

写出4位二进制加法计数器的VHDL语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CNT4 IS

PORT (CLK: IN BIT;

Q:BUFFER INTEGER RANGE 15 DOWNTO 0);

END CNT4;

ARCHITECTURE BHV OF CNT4 IS

BEGIN

PROCESS (CLK)

BEGIN

IF CLK'ENENT AND CLK='1' THEN Q<=Q+1;

END IF;

END PROCESS;

END BHV;

移位寄存器

写出带有同步预置控制的8位 右移 移位寄存器的VHDL代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SHFT IS

PORT (CLK,LOAD: IN STD_LOGIC;

QB:OUT STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END SHFT;

ARCHITECTURE BEHAV OF SHFT IS

SIGNAL REG8 :STD_LOGIC_VECTOR(7 DOWNTO 0)

BEGIN

PROCESS (CLK,LOAD)

BEGIN

IF CLK'ENENT AND CLK='1' THEN

IF LOAD ='1' THEN

REG8 <= DIN;

ELSE REG8(6 DOWNTO 0) <= REG(7 DOWNTO 1);

END IF;

END IF;

END PROCESS;

QB <=REG8(0);

DOUT<=REG8;

END BEHAV;

三态控制门电路

写出8位三态控制门电路的VHDL描述语言代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY tri_s IS

port (enable : IN STD_LOGIC;

datain : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

dataout : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END tri_s ,;

ARCHITECTURE bhv OF tri_s IS

BEGIN

PROCESS(enable,datain) BEGIN

IF enable=,11 THEN dataout <= datain ;

ELSE dataout <="ZZZZZZZZ" ; END IF ;

END PROCESS;

END bhv;