本文最后更新于 1577 天前,其中的信息可能已经有所发展或是发生改变。

写在前面

VHDL课要学这个东西,而且我也想玩主要是(有哪个可爱的小朋友不喜欢好看的连连看工具呢?

但是在学校机房是事先安装好的,一点都不好玩

因此想的自己的电脑上装一下

然后发现这个破软件巨难装

Quartus 各个版本区别

Quartus II 已经算是老版本了

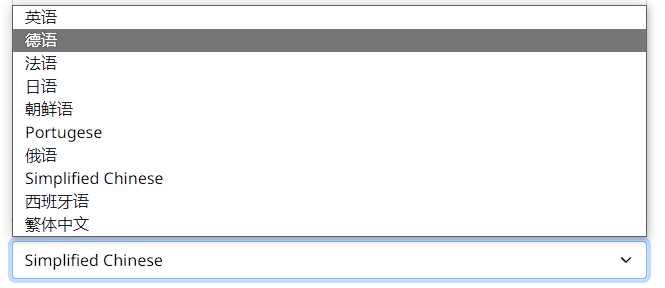

学校教的是 18.1,然而这个教程是 21.3

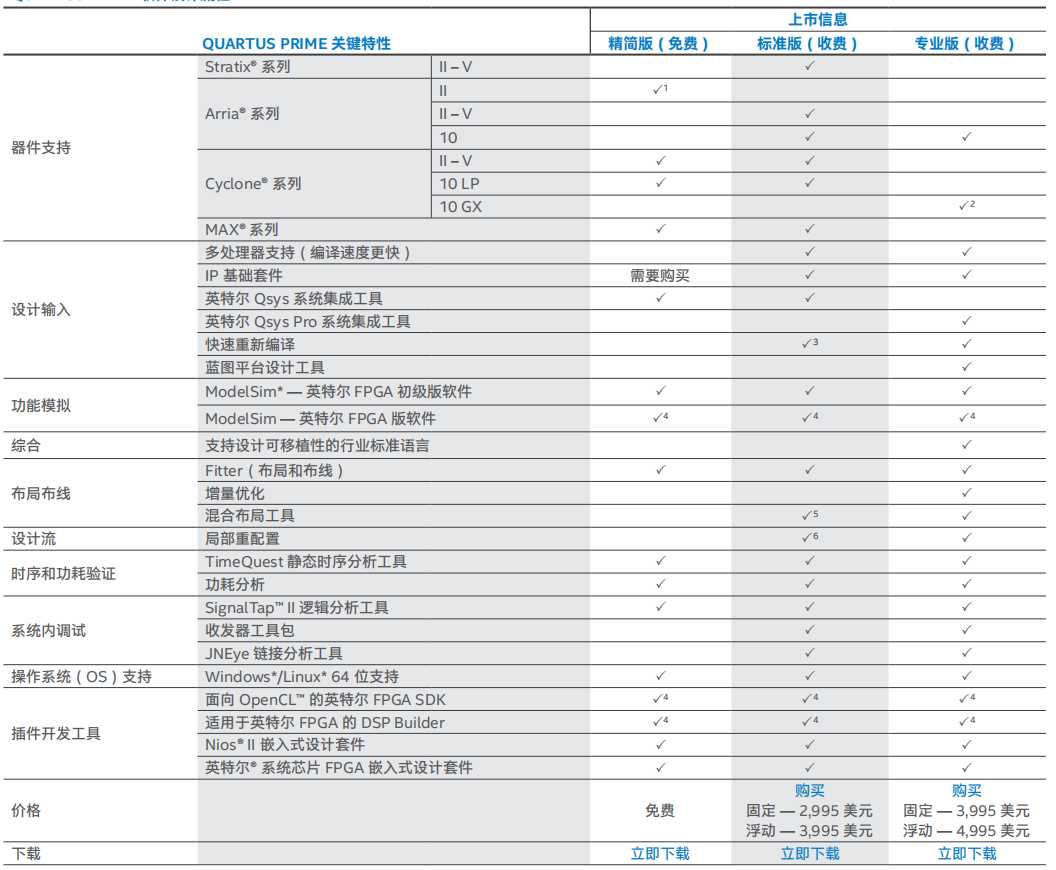

Quartus 有精简版、标准版、PRO 之分。

从这开始看

上面的都是废话,从这里开始,内容只针对期末考

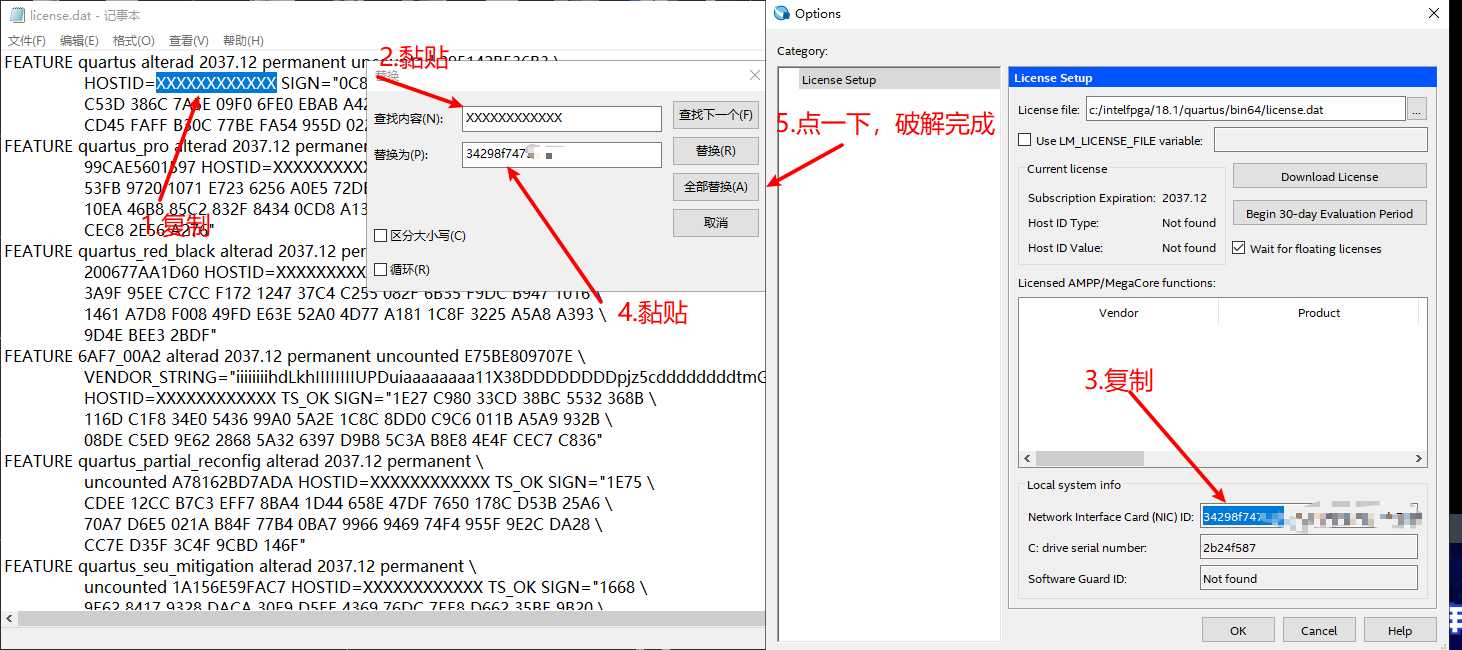

破解

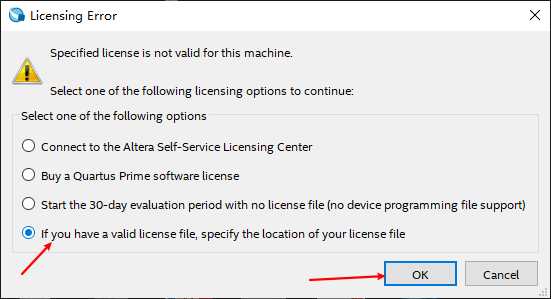

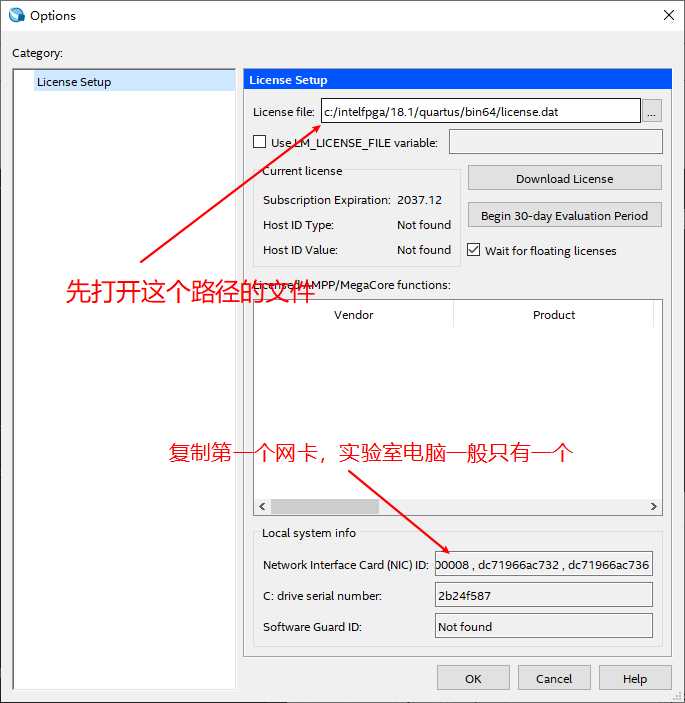

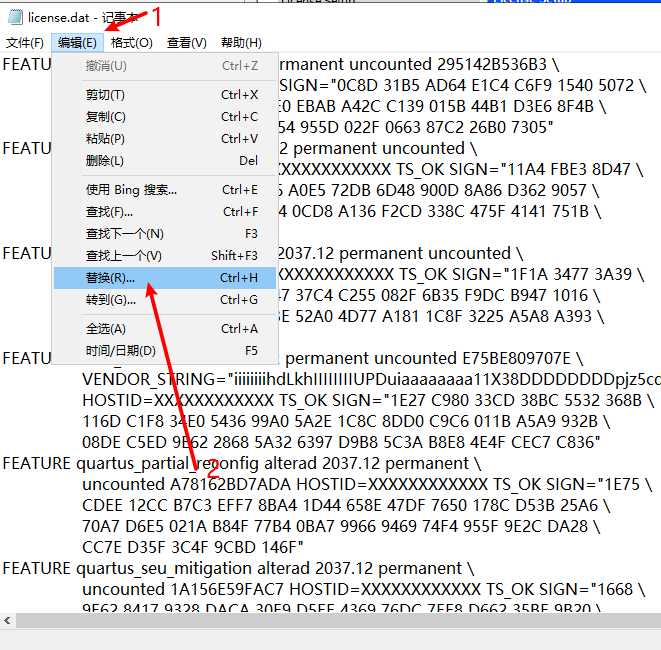

点开 Quartus 的图标

然后重新打开软件,就发现破解完成了。

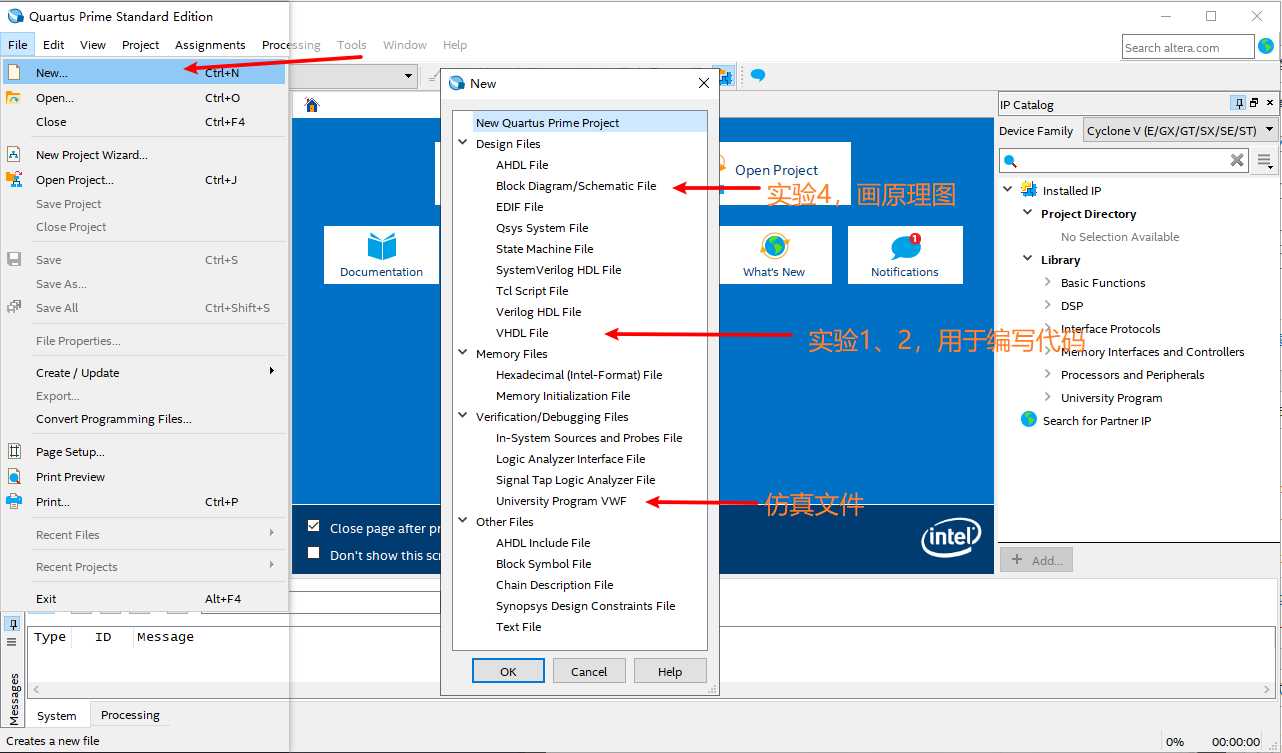

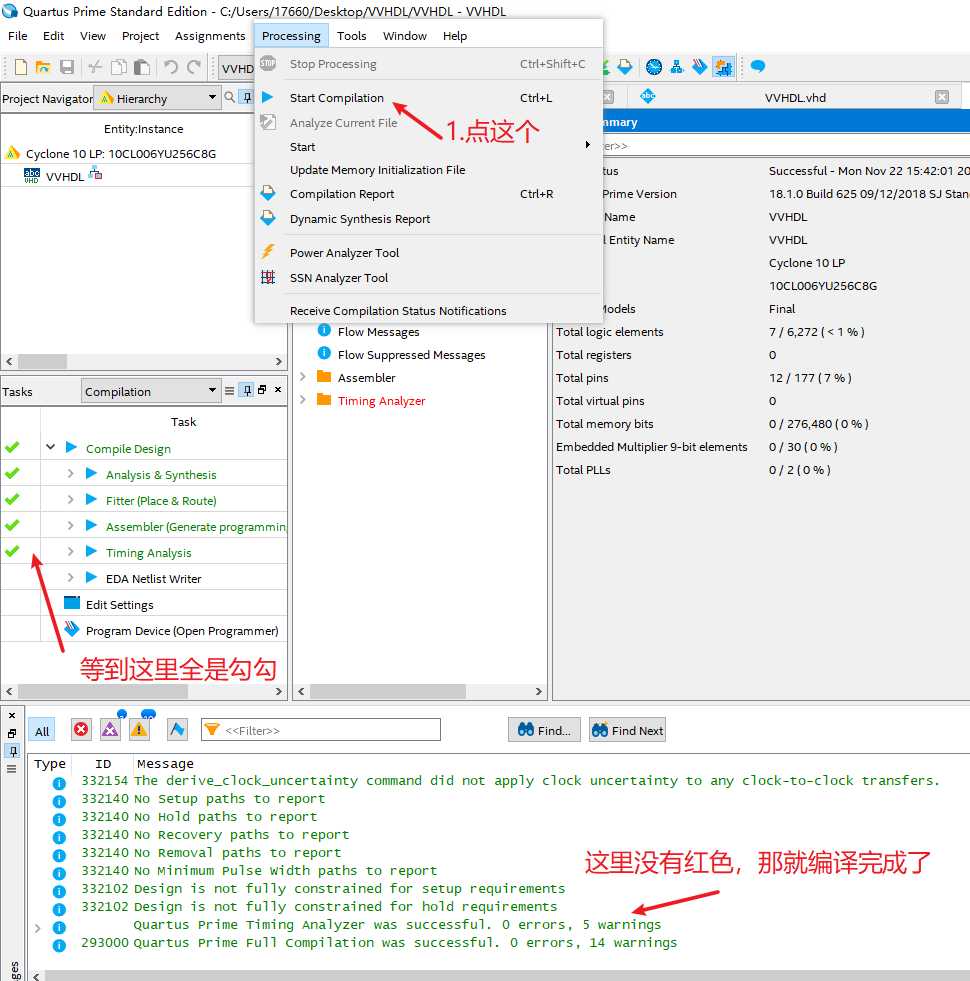

考试用到的重要按钮

记住,对你来说这不是一个复杂的开发工具,而是一个类似于爱奇艺那样点几下就能看到易烊千玺的软件:yum:

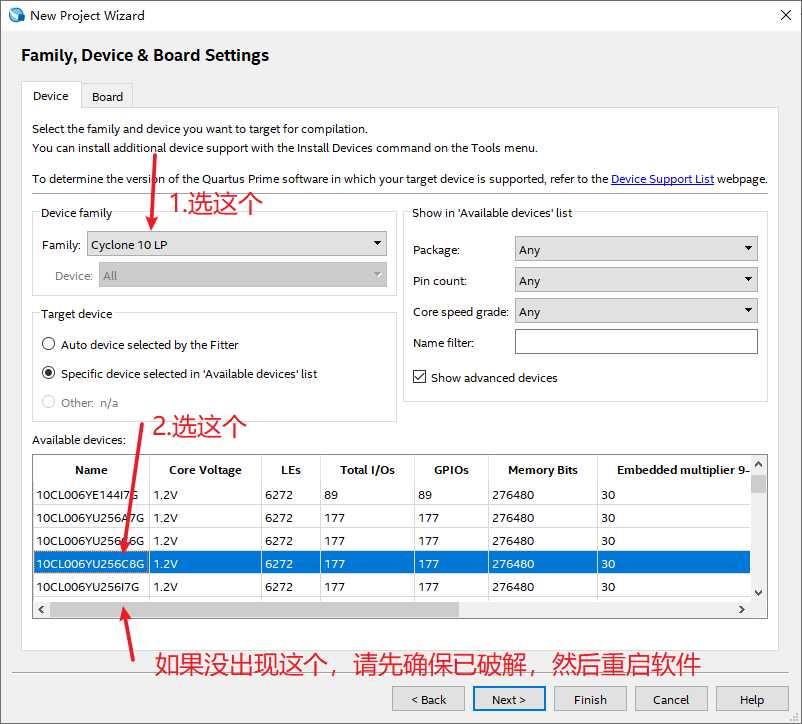

然后点一个 YES ,然后一路 NEXT。

那个芯片不要去死记,就记住 第 10 季,006 集,256分钟,第 8 秒出现易烊千玺(doge。

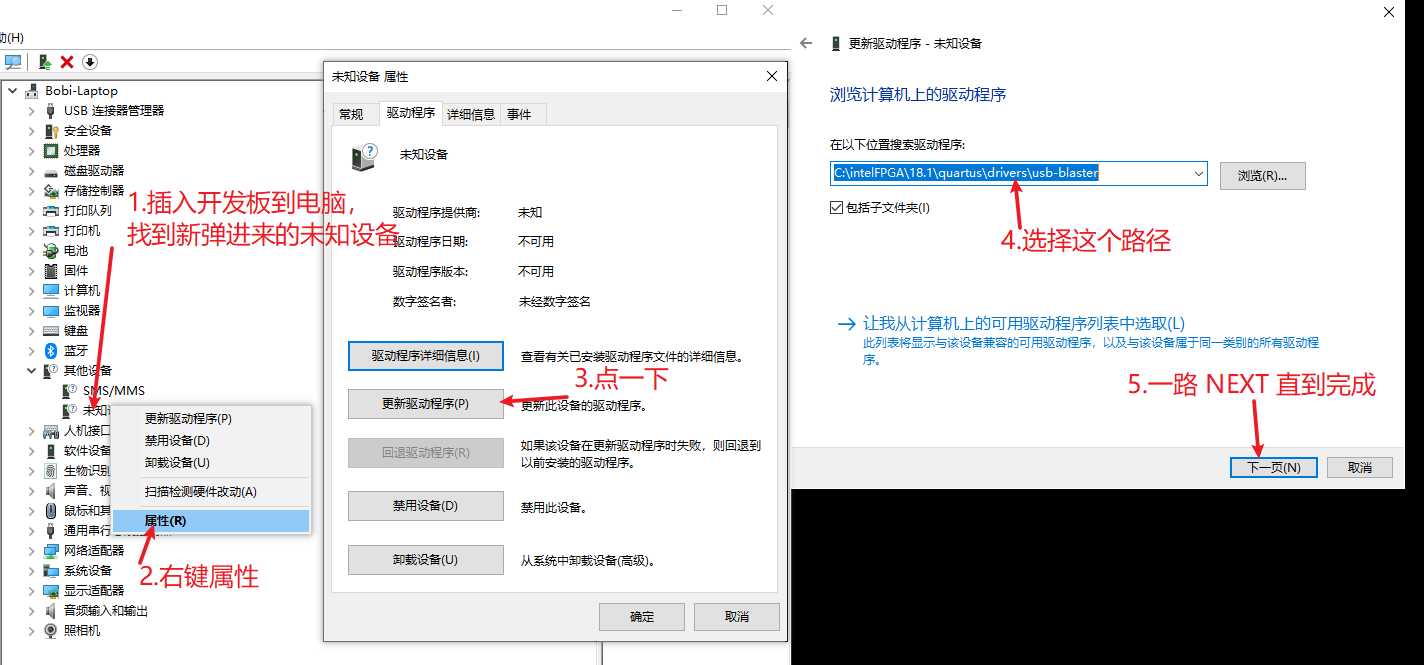

6.安装烧录器驱动

由于现在 Bobi 没有开发板,所以有些部分只能意思意思,但是精髓都说了

路径如下

C:\intelFPGA\18.1\quartus\drivers\usb-blaster

实验题

实验1

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECL7S IS

PORT(A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B : OUT STD_LOGIC;

LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END;

ARCHITECTURE ONE OF DECL7S IS

BEGIN

PROCESS(A)

BEGIN

CASE A IS

WHEN "0000" => LED7S <= "1000000";

WHEN "0001" => LED7S <= "1111001";

WHEN "0010" => LED7S <= "0100100";

WHEN "0011" => LED7S <= "0110000";

WHEN "0100" => LED7S <= "0011001";

WHEN "0101" => LED7S <= "0010010";

WHEN "0110" => LED7S <= "0000010";

WHEN "0111" => LED7S <= "1111000";

WHEN "1000" => LED7S <= "0000000";

WHEN "1001" => LED7S <= "0010000";

WHEN "1010" => LED7S <= "0001000";

WHEN "1011" => LED7S <= "0000011";

WHEN "1100" => LED7S <= "1000110";

WHEN "1101" => LED7S <= "0100001";

WHEN "1110" => LED7S <= "0000110";

WHEN "1111" => LED7S <= "0001110";

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

B <= '0';

END;

实验2

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DOCODER38 IS

PORT{

A: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

ST,STAL,STBL:IN STD_LOGIC;

Y : OUT STDD_LOGIC_VECTOR(7 DOWNTO 0);

};

END ENTITY DECODR38 ;

ARCHITECTURE ARCH_DOCODER38 OF DECODER38 IS

BEGIN

PROCESS(A)

BEGIN

IF ST="1" AND STAL="0" AND STBL= "0" THEN

CASE (A) IS

WHEN "000"=> Y<="11111110";

WHEN "001"=> Y<="11111101";

WHEN "010"=> Y<="11111011";

WHEN "011"=> Y<="11110111";

WHEN "100"=> Y<="11101111";

WHEN "101"=> Y<="11011111";

WHEN "110"=> Y<="10111111";

WHEN (OTHERS)=> Y<="01111111";

END CASE;

ELSE Y<="1111111";

END IF;

END PROCESS;

END ARCHITECTURE ARCH_DOCODER38;