# 写在前面

本文内容由《嵌入式系统体系、原理与设计》课后习题、老师部分 PPT、老师布置的学习崩作业等组成,主要目的是为了在考试前预习一下该科目。

其中,课后习题部分非常感谢 http://m.elecfans.com/article/1718269.html 的帮助!!!

判断题(10道)x1分

单选题(10道)x2分

多选题(5道)x4分(多选不得分,漏选得一半分)

简答题 (3道)总共30分

代码填入题 (2道)总共20分

单选题

1.下面关于嵌入式系统使用的存储器的叙述中,错误的是( 存储容量大几十GB的微硬盘,其内部的储存器主要是Flash ROM )

2.下面关于嵌入式系统的存储器的叙述中,错误的是( 嵌入式系统的主存储器是指嵌入式处理器内部的存储器 )

3.嵌入式系统的软件大多存储在非易失性的存储器中,即时断电也不会消失。目前嵌入式系统使用最多的非易失性存储器是( Flash Memory )

4.供电电路中,滤波电路功能是:( 滤除单向脉动电流中的交流成分 )

5.STM32中通过总线与其他硬件组件连接在一起,下面出的4个组件中,哪一个组件是挂在APB总线上的?( PWM )

6.下面是关于嵌入式硬件系统的电源电路的描述,其中错误的是( LDO(low dropout regulator)是一种完成交流电到直流电交换的模块 )

7.下面关于嵌入式最小硬件系统的叙述中,错误的是( 嵌入式最小系统包括复位电路,嵌入式处理器的复位引脚为nRESET时,表示高电平复位 )

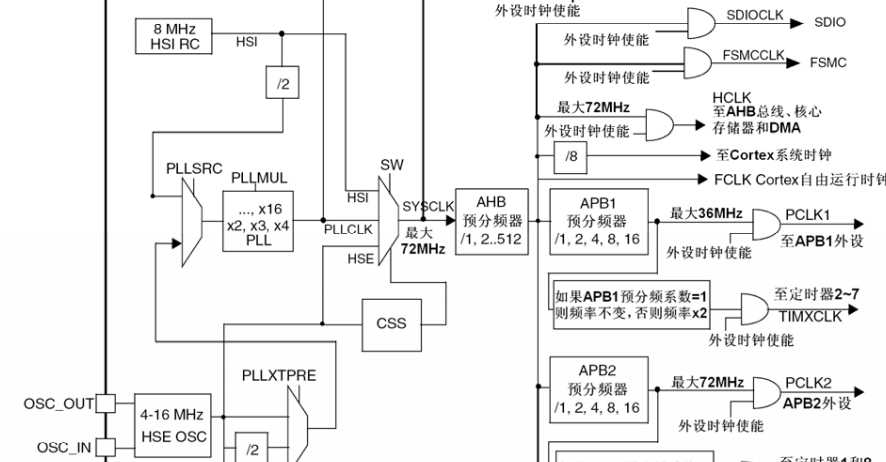

8.关于 STM32F103 中时钟电路正确的是( 内部包含了 8MHz 的高速内部时钟 )

9.下列关于软件复位不正确的是( 系统级复位前,并不需要屏蔽中断请求 )

10.下列不属于嵌入式系统的共性特点的是( 技术途径狭窄 )

11.以下不属于嵌入式系统的是( 笔记本电脑 )

12.想要 OD 门(漏极开路)输出有效的高电平和低电平,应该需要下列什么措施( 上拉电阻 )

13.推挽电路组成为( P-Mos 和 N-MOS )

14.供电电路中,滤波电路功能是( 滤除单向脉动电流中的交流成分 )

15.下列关于 bootloader 的说法错误的是( Bootloader 执行的第一条指令必须存储在 RAM 存储器中 )

16.嵌入式系统的开发有一些不同于通用计算机应用开发的特点,下面不属于嵌入式系统开发特点的是( 应用软件必须在基于嵌入式操作系统平台上来开发 )

17.以下关于嵌入式系统软件与通用计算机系统软件的异同的叙述中,正确的事( 嵌入式系统应用软件往往内部结构精简化、代码轻量化、占用存储资源少 )

18.下列关于嵌入式系统硬件抽象层的描述中,正确的是( 硬件抽象层向操作系统内核提供了访问底层硬件的函数接口 )

19.下面关于嵌入式最小硬件系统的叙述中,错误的是( 嵌入式处理器必须扩展外部存储器才能组成正常工作的嵌入式最小系统 )

多选题

1.最小系统外围电路包括以下哪些( 电源电路、时钟电路、复位电路 )

2.以下关于复位的说法,正确的是( 系统上电后,对必要的寄存器,I/O接口等资源的值和状态进行初始化;复位后,电路进入一个预先设置的已知就绪状态;系统掉电后,也需要进行复位操作 )

3.关于看门狗复位电路正确的是:( ABCD; 看门狗监控系统程序,当监控到异常时,自动进行复位;看门狗复位电路需要定时执行喂狗操作;看门狗复位电路能够通过计数器实现;看门狗复位电路能够通过专用的看门狗芯片实现 )

4.关于看门狗复位电路正确的是( ABCD;看门狗复位电路需要定时执行喂狗操作;看门狗复位电路能够通过计数器实现;看门狗复位电路能够通过专门的看门狗芯片实现;看门狗监控系统程序,当监控到异常时,自动进行复位 )

5.RC 复位电路的典型改进方法有( 在复位信号上接入反相器;在电阻两旁加入二极管 )

6.寄存器可以暂存计算过程中的( 指令;数据;地址 )

7.系统时钟来源可以有( 高速外部时钟;内部时钟;低速外部时钟 )??期中多选4

8.关于冯·诺依曼结构正确的是( 较低的数据吞吐量;程序指令和数据存储在同一存储器中 )

9.最小系统外围电路包括以下哪些( 复位电路;电源电路;时钟电路 )

10.以下关于复位的说法正确的是( 复位后,电路进入一个预先设置的已知就绪状态;系统掉电后,也需要进行复位操作;系统上电后,对必要的寄存器,IO接口等资源的值和状态进行初始化 )

判断题

对的

1.嵌入式系统的工作频率越高,越耗电

2.三态输出包含高电平、低电平和浮动三种状态。

3.

4.

5.印制电路板中,元件封装形式需要跟实际使用的芯片封装形式相同

6.智能手表属于嵌入式系统

7.ARM架构采用RISC类型的处理器架构,指令长度保持一致

8.哈佛结构能够提供更大的储存器带宽

9.ARM处理器同时只能支持ARM指令集和16位Thumb指令中的一种??

10.上拉电阻可以讲引脚信号钳位在高电平

11.哈佛结构采用独立的存储器分别存储程序指令与数据??

12.在电路原理图中,可以连接不同的器件??

13.退藕电容可以放在输入电压旁,当供电能力不足时,提供电容

14.解决驱动过载的问题需要增加额外的驱动电路或逻辑

15.OC 输出需要外接上拉电阻,否则不能输出有效的低电平??

错的

1.Sepic电路是一种升压电路,仅能够允许输出电压大于输入电压。

2.在印制电路板中,可以自由调整元件布放位置

3.siri 语言助手属于嵌入式系统

3.Sepic电路是一种升压电路,仅能够允许输出电压大于输入电压

4.任何时候,芯片引脚的信号要么为高要么为低

5.下拉电阻可以在驱动能力不足的时候提供电流

6.总线竞争是不良竞争,可以通过推挽电路进行设计避免

7.退耦电容可以放在信号输入端,滤除高频噪声

填空题

1.Flash中根据内部存储元的组织结构和特性,可以将Flash分为( NOR )Flash 和( NAND )Flash

2.工作时随时可以进行数据读出或写入的存储器件为( RAM ),RAM可以分为( SRAM )和( DRAM )

代码题

1.请分析以下代码的软件结构,解释为什么是该软件结构。并且结合实际讨论该软件结构的优缺点。

void USART1_IRQHandler(void) //串口1 中断服务程序

{

unsigned int i;

if(USART_GetlTStatus(USART1,USART_IT_RXNE) != RESET)//判断读寄存器是否非空

{

RxBuffer1[RxCounter1++] = USART_ReceiveData(USART1);//将读寄存器的数据缓存到接收缓冲区里

if(RxBuffer1[RxCounter1-2]==0x0d&&RxBuffer1[RxCounter1-1]==0x0a)//判断结束标志是否是0x0d Ox0a

for(i=0; i< RxCounter1; i++) TxBuffer1[i] =RxBuffer1[i]; //将接收缓冲器的数据转到发送缓冲区,准备转发

rec_f=1;//接收成功标志

TxBuffer1[RxCounter1]=0;

//发送缓冲区结束符

RxCounter1=0;

int main(void)

uint8_t a=0,b=0;

/* System Clocks Configuration */

RCC_Configuration();//系统时钟设置

/嵌套向量中断控制器

配置了USART1的优先级分组为0,抢占优先级级别0(无),和响应优先级级别0(0-7)*/NVIC_Configuration();//中断源配置

/* 对控制LED指示灯的10口进行了初始化,将端口配置为推挽上拉输出,口线速度为50Mhz。PA9,PA10端口复用为串口1的TX,RX。

在配置某个口线时,首先应对它所在的端口的时钟进行使能。否则无法配置成功,由于用到了端口B,因此要对这个端口的时钟

进行使能,同时由于用到复用10口功能用于配置串口。因此还要使能AFIO(复用功能IO)时钟。*/

GPIO_Configuration0;//端口初始化

USART_Config(USART1);//串口1初始化

USART_OUT(USART1,"****(C) COPYRIGHT2013奋斗嵌入式开发工作室*******r\n"); 11向串口1发送开机字符。

while(1)

if(rec_f==1)(//判断是否收到一帧有效数据rec_f=0;

USART_OUT(USART1,"Ir\n您发送的信息为:\r\n");

USART OUT(USART1,&TxBuffer1[0]);

if(a==0) (GPIO_SetBits(GPIOB,GPIO_Pin_5);a=1; //LED1 V6 (V3V5板)V2 (MINI板)明暗闪烁

else (GPIO_ResetBits(GPIOB, GPIO_Pin_5);a=0;

if(b==0) (GPIO_SetBits(GPIOD,

GPIO_Pin_3|GPIO_Pin_6);b=1; //LED1

V6(V3V5板)V2(MINI板)明暗闪烁

else [GPIO ResetBits(GPIOD,

GPIO_Pin_3|GPIO_Pin_6);b=0;

)

轮转结构:软件中仅有一个循环结构的代码在执行,该段循环代码顺序查询条件,执行相应分支。

优点:

最简单的结构;

结构中不存在中断,没有数据共享;

主循环简单地依次检查每个I/O设备,为其提供服务;

缺点:

不同I/O要求不同的响应速度,轮转结构很难保证;

当分支处理时间达到数秒级时,操作响应变慢;

设备增加,时间片将可能变小,单个分支响应变慢;

CPU全速运行,功耗大,电池供电系统难以承受;

带有中断的轮转结构:中断程序可以处理硬件特别紧急的需求,然后设标志;轮询程序是后台,负责具体事务;中断程序是前台,负责检查服务请求;

优点:

较轮转方式增强了优先级处理能力

中断程序较主程序有更好优先级;

中断具有优先级属性,可设置;

优先级高的请求将及时得到响应,而普通轮转结构只能按顺序响应;

缺点:

任务代码以同样优先级顺序执行,中断优先级体现的不够明显;

另一个问题,任务代码全速运行,没有达到节能目的!

基于定时器中断的轮转软件结构(中断事件驱动系统):主程序进行系统初始化,设置并启动定时器中断;定时器中断程序中轮询完成事务处理;整个嵌入式系统软件由中断服务程序构成;

构成:

主程序与多个中断服务例程;

中断不能过多,否则可能导致某些中断不能及时被响应;

优点:

较前两种方式更加节能;

缺点:

和方式一一样只能顺序处理;

中断间隔过短可能造成等待,过长可能降低系统灵敏度;

不易扩展,增加新的事务,要重新计算时间;

函数队列调度结构:中断程序不做具体事务处理,只在函数指针队列中添加相应的函数指针,供main调用;

主程序仅需从该队列中读取相应指针并调用相关函数即可;

最高优先级中断代码的最坏响应时间等于最长任务代码执行时间;

优点:

与轮转结构、带中断的轮转结构相比,main不再按照严格的顺序来执行;

只需对函数指针进行排队过程进行调整,即可依据任何可达目标的优先级方案来调用函数;

缺点:

需要维护函数指针队列;

低优先级函数可能永远都不能执行

2.中断设置是入式系统任务管理的基本功前,请规理以下库函数以及注释填写对应代码

void NVIC_Configuration(void)

{

/* 结构声明*/

NVIC_InitTypeDef NVIC_InitStructure;

/* Configure the NVIC Preemption Priority Bits */

/* Configure one bit for preemption priority */

/* 优先级组 说明了抢占优先级所用的位数,和响应优先级所用的位数 在这里是0, 4

0组: 抢占优先级占0位, 响应优先级占4位

1组: 抢占优先级占1位, 响应优先级占3位

2组: 抢占优先级占2位, 响应优先级占2位

3组: 抢占优先级占3位, 响应优先级占1位

4组: 抢占优先级占4位, 响应优先级占0位

*/

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0);

NVIC_InitStructure.NVIC_IRQChannel = USART1_IRQn; //设置串口1中断

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; //抢占优先级 0

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; //子优先级为0

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能

NVIC_Init(&NVIC_InitStructure); //初始化

}

3.中断设置是入式系统任务管理的基本功前,请规理以下库函数以及注释填写对应代码

void NVIC_Configuration(void)

{

NVIC_InitTypeDef NVIC_InitStructure;

EXTI_InitTypeDef EXTI_InitStructure;

/* Configure one bit for preemption priority */

/* 优先级组 说明了抢占优先级所用的位数,和响应优先级所用的位数 在这里是1, 3

0组: 抢占优先级占0位, 响应优先级占4位

1组: 抢占优先级占1位, 响应优先级占3位

2组: 抢占优先级占2位, 响应优先级占2位

3组: 抢占优先级占3位, 响应优先级占1位

4组: 抢占优先级占4位, 响应优先级占0位 */

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

/* Enable the EXTI9-5 Interrupt */

NVIC_InitStructure.NVIC_IRQChannel =EXTI9_5_IRQn; //外部中断9-5

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; //抢占优先级 0

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1; //子优先级1

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能

NVIC_Init(&NVIC_InitStructure);

//用于配置AFIO外部中断配置寄存器AFIO_EXTICR1,用于选择EXTI5外部中断的输入源是PC5。

GPIO_EXTILineConfig(GPIO_PortSourceGPIOC, GPIO_PinSource5); //外部中断配置AFIO--ETXI9-5

//用于配置AFIO外部中断配置寄存器AFIO_EXTICR1,用于选择EXTI2外部中断的输入源是PC2。

GPIO_EXTILineConfig(GPIO_PortSourceGPIOC, GPIO_PinSource2); //外部中断配置AFIO--ETXI2

EXTI_InitStructure.EXTI_Line = EXTI_Line5; //PC5 作为键盘K1 检测状态

EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt; //中断模式

EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling; //下降沿触发

EXTI_InitStructure.EXTI_LineCmd = ENABLE;

EXTI_Init(&EXTI_InitStructure);

}

4.通信协议的配置是嵌入式系统与外界通讯的基本功能,请根据以下库函效以及注释填写对应代码

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9; //设置 PA9 为 TX

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //推挽输出

GPIO_Init(GPIOA, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10; //设置 PA10 为 RX

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; //输入浮空模式

GPIO_Init(GPIOA, &GPIO_InitStructure);

void USART_Config(USART_TypeDef* USARTx)

{

GPIO_InitTypeDef GPIO_InitStructure;

USART_InitTypeDef USART_InitStruct;

USART_ClockInitTypeDef USART_ClockInitStruct; //定义 USART 结构体变量

USART_InitStructure.USART_BaudRate = 115200; //速率 115200bps

USART_InitStructure.USART_WordLength = USART_WordLength_8b; //数据位 8 位

USART_InitStructure.USART_StopBits = USART_StopBits_1; //停止位 1 位

USART_InitStructure.USART_Parity = USART_Parity_No; //无校验位

USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None; //无硬件流控

USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx; //收发模式

/* Configure USART1 */

USART_Init(USARTx, &USART_InitStructure); //配置串口参数函数

/* Enable USART1 Receive and Transmit interrupts */

/* 启用 USART1 接收和发送中断 */

USART_ITConfig(USART1, USART_IT_RXNE, ENABLE); //使能接收中断

USART_ITConfig(USART1, USART_IT_TXE, ENABLE); //使能发送缓冲空中断

USART_ITConfig(USART1,USART_IT_TC,ENABLE); //使能发送中断

/* Enable the USART1 */

USART_Cmd(USART1, ENABLE); //使能 USARTx

USART_SendData(USARTx, *Data); //调用发送函数

Data = USART_ReceiveData(USARTx); //调用接受函数

USART_GetFlagStatus(USARTx, USART_FLAG_TC)==RESET //收发状态函数,判断发送是否完成

/* 若前面无声明此函数 需要加 viod */

USART_ReceiveData(USART_TypeDef* USARTx); //寄存器读取串口接收到的数据

/* 若前面无声明此函数 需要加 uint16_t */

void USART_DeInit(USART_TypeDef* USARTx);//串口复位

}

5.配置 GPIO 口,请根据以下库函效以及注释填写对应代码

void GPIO_Configuration(void)

{

GPIO_InitTypeDef GPIO_InitStructure; //定义GPIO_InitTypeDef结构体变量

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_5; //LED1 V6

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; //推挽输出

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; //端口速率 50MHz

GPIO_Init(GPIOB, &GPIO_InitStructure); //输入初始化函数PB的地址,和结构体具体变量

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6|GPIO_Pin_3; //LED2, LED3 V7 V8

GPIO_Init(GPIOD, &GPIO_InitStructure);

GPIO_SetBits(GPIOB, GPIO_Pin_5); //LED1 亮,设置引脚高电平

GPIO_SetBits(GPIOD, GPIO_Pin_6|GPIO_Pin_3 ); //LED2,LED3亮

GPIO_ResetBits(GPIOB, GPIO_Pin_5); //设置引脚低电平

Delay(0xAFFFF); //延迟 720895ms 0X为 16 进制 0O为 8 进制

/* K1 配置按键中断线PC5 */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_5;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU; //输入上拉

GPIO_Init(GPIOC, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13; //LCD背光控制

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;

GPIO_Init(GPIOD, &GPIO_InitStructure);

GPIO_ResetBits(GPIOD, GPIO_Pin_13); //LCD背光关闭

}

简答题

1.为什么复位电路需要进行掉电检测?请简要说明理由,并阐述 RC 复位电路的优缺点

许多IC都包含上电复位(POR)电路,其作用是保证在施加电源后,模拟和数字模块初始化至已知状态。基本上电复位(POR)功能会产生一个内部复位脉冲以避免”竞争”现象,并使器件保持静态,直至电源电压达到一个能保证正常工作的阈值。上电复位(POR)电路有时会集成一个掉电检测器(BOD),用于防止电路在电压非常短暂地意外降低时发生复位,从而避免故障。

RC 复位电路的优点:实现简单,需要的元器件少,大部分时间正常工作

缺点:1.上电时存在因滤波电容等引起的电压建立延迟时间,以及电压上升到逻辑高电平后振荡器从偏置、起振、锁定到稳定的时钟建立延迟时间,整个复位脉冲的宽度必须大于这些时间的总和。

2.在电源瞬时跌落和恢复的过程中,电容充放电的指数特性导致电容未完成放电时便开始充电,从而无法缠上宽度合格的复位脉冲

2.上图为 STM32 的时钟树,请问采用内部时钟 8MHz,想要将 SYSCLK 设置为 72MHz,PCLK1 设置为 36Mhz,怎么进行设置

3.请详细说明 bootloader 的两阶段启动过程,并分析其针对于单阶段启动的优缺点

第一阶段功能

(1)硬件设备初始化

(2)为加载bootloader的第二个阶段代码准备RAM空间

(3)复制bootloader的第二个阶段代码到RAM中

(4)设置好栈

(5)跳转到第二阶段代码的C入口点

第二个阶段的功能

(1)初始化本阶段要使用到的硬件设备

(2)检测系统内存映射

(3)讲内核映像和根文件系统从Flash上读到RAM空间中

(4)为内核设置启动参数

(5)调用内核

单阶段 Bootloader 的代码量通常非常小,其功能也就比较简单

两阶段 Bootloader 在第二阶段在内存中运行,不在受到内存容量的限制,因而允许设计更为复杂的功能

3.中断及其数据共享问题:vUpdateTime例子如何消除数据共享问题

1.基于开关中断主程序优化方案,禁止中断和使能中单保证了访问共享变量的原子性,从而消除了数据共享问题;但是并不适合多个并发任务同时调用

2.引入一个新的全局变量 count 初值为 0,任何人物在禁止中断语句后都需要对 count 加 1 操作,表示当前进入一个处于临界区状态任务,在该任务结束后 count 减 1,表示该任务离开了临界区。通过判断 count 的值便可判断是否有任务处于临界区执行。

3.将 lSecondsToday 设置为共享变量,由中断服务程序计算 lSecondsToday 的值,并在 ISecondsSinceMidnight() 中使用。

4.在函数 ISecondsSinceMidnight() 中增加一个 while 循环,在函数运行时,执行 lReturn=lSecondsToday;赋值之后,while 循环会判断之前的值与当前的值是否相等,如果不相等则重复读取变量并判断,否则读取数据有效,退出循环。

课后习题

第零章 按照考纲写重点笔记

注意:本章内容为按照考纲的内容,但是乱序!

1.抢占优先级与响应优先级的区别

高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的

抢占优先级相同的中断,高响应优先级不可以打断低响应优先级的中断

抢占优先级相同的中断,当两个中断同时发生的情况下哪个响应优先级高,哪个先执行

连个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行

2. USART

USART: (Universal Synchronous/Asynchronous Receiver / Transmitter)即通用同步/异步串行接收/发送器是一个全双工通用同步/异步串行收发模块,该接口是一个高度灵活的串行通信设备。

USART 收发模块一般分为三大部分:时钟发生器、数据发送器和接收器。控制寄存器为所有的模块共享。

TTL: 1:2.4-5v 0:0-0.5v

由启始位、主体数据、校验位以及停止位组成

1、总线在发送或接收前应处于空闲状态

2、串口通讯的一个数据包从起始信号开始,直到停止信号结束。数据包的起始信号由一个逻辑0的数据位表示,而数据包的停止信号可由0.5、1、1.5或2个逻辑1的数据位表示,只要双方约定一致即可。

3、 一个数据字( 8位或者9位)

4、在有效数据之后,有一个可选的数据校验位

5、使用分数波特率产生器–带12位整数和4位小数

RX:接收数据输入是串行数据输入。

TX:发送数据输出。不发数据的时候是高电平

在同步模式中需要下列引脚:

SCLK: 发送器时钟输出。

在IrDA模式中需要下列引脚:

IrDA_RDI:数据输入就是IrDA模式下的数据输入。

IrDA_TDO: IrDA模式下的数据输出。

在调制解调器模式中需要下列引脚:

nCTS: 清除发送

nRTS: 发送请求

串口设置一般可以总结为如下几个步骤:

1、串口时钟使能, GPIO 时钟使能

2、串口复位

3、GPIO 端口模式设置

4、串口参数初始化

5、开启中断并且初始化 NVIC(如果需要开启中断才需要这个步骤)

6、使能串口

7、编写中断处理函数

1、波特率控制

波特率,即每秒传输的二进制位数,用 b/s (bps)表示,通过对时钟的控制可以改变波特率。在配置波特率时,我们向波特比率寄存器 USART_BRR 写入参数,修改了串口时钟的分频值 USARTDIV。USART_BRR 寄存器包括两部分,分别是 DIV_Mantissa(USARTDIV 的整数部分)和 DIVFraction(USARTDIV的小数)部分,最终,计算公式为:

USARTDIV = DIV_Mantissa + (DIVFraction / 16)。

2、分数波特率的产生

接收器和发送器的波特率在USARTDIV的整数和小数寄存器中的值应设置成相同。

Tx / Rx 波特率 = fCK / (16 * USARTDIV)

这里的fCK是给外设的时钟(PCLK1用于USART2、3、4、5,PCLK2用于USART1) USARTDIV是一个无符号的定点数。这12位的值设置在USART_BRR寄存器。

注: 在写入USART_BRR之后,波特率计数器会被波特率寄存器的新值替换。因此,不要在通信进行中改变波特率寄存器的数值。

USARTDIV 是对串口外设的时钟源进行分频的,对于 USART1,由于它是挂载在 APB2 总线上的,所以它的时钟源为 fPCLK2;而 USART2、3 挂载在APB1 上,时钟源则为 fPCLK1,串口的时钟源经过 USARTDIV 分频后分别输出作为发送器时钟及接收器时钟,控制发送和接收的时序。

3.RS232 与 RS422

RS232: 1:-12v~-3v 0:+3v~+12v

RS232物理接口:无明确规定,有 9 针 DB9、25 针 DB25 、8针 RJ45

RS232 与 UART 连接,需要 MAX232 等芯片实现 COMS / TTL 电平与 232 电平进行转换

RS232优点:可以简单的实现与外部设备的串行双工通信

缺点:采用单端通信模式,接口信号电平高、线路抗干扰能力差、只适用于距离近速率低的数据通信。

RS-422 每个数据通道的 RxD、TxD 分别由 RxD+、RxD- 和 TxD+、TxD- 两组引脚共 4 条信号线组成。。发送方的 TxD+ TxD- 引脚对应连接接收方的 RxD+ RxD- 引脚,分别传输信号的正逻辑和负逻辑。

0:<-200mv ; 1:>+200mv

RS-422 是一个 200kbps 的差分反相通信线路,使用双绞线作为互联介质。差分信号传输方式大大增强了通信信道的抗干扰能力和数据传输的可靠性,最大速率可达 10Mbps,1200m。

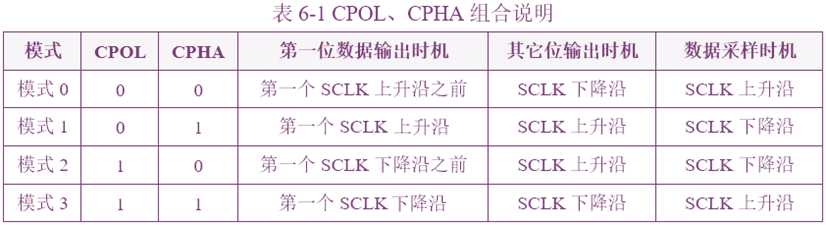

3.SPI

串行外设接口是一种简单的基于位同步的一主多从式、全双工串行通信总线标准,主要用于连接嵌入式处理器与 SD 卡、LED、传感器、FLASH、Wifi模块等系统 I/O 设备,通信速率可达数十 Mb/s。

PD端口的4引脚实现数据传送

串行时钟SPSCK/PD3

主接收从发送 MISO/PD1

主发送从接收 MOSI/PD2

低有效从机片选SS/PD0;

不用 SPI功能时,这些引脚被配置成通用并行输入线;

主机模式中:发出时钟写数据到数据寄存器移位寄存器移位完成后状态位自动置位;

从机模式中:等待 SS 拉低,通过 SPSCK 与主机同步;

5.GPIO

8种工作模式:

输入浮空模式 GPIO_Mode_IN_FLOATING =0x04

输入上拉模式 GPIO_Mode_IPU =0x48

输入下拉模式 GPIO_Mode_IPD =0x28

输入模拟模式 GPIO_Mode_AIN =0x0

开漏输出模式 GPIO_Mode_Out_OD=0x14

复用开漏输出模式 GPIO_Mode_AF_OD=0x1c

推挽输出模式 GPIO_Mode_Out_PP=0x10

复用推挽输出模式 GPIO_Mode_AF_PP=0x18

输入端口模式:需要禁止输出缓冲区,激活施密特触发器的输入,根据上拉/下拉电阻寄存器 GPIOx_PUPDR 的配置激活上拉或下拉电阻。在每个 AHB 时钟周期,该引脚上出现的数据将被采样到输入数据寄存器,而对输入数据寄存器的访问操作将返回一个 I/O 状态。

输出端口模式:需要使能输出缓冲区,激活施密特触发器,并根据 GPIOx_PUPDR 决定是否激活弱的上拉/下拉电阻。每个 AHB 时钟周期,该引脚的数据将被采样到输入数据寄存器,读输入数据寄存器的操作会返回引脚状态,而读输出数据寄存器可以获得最近写入的值。在开漏输出模式下, P-MOS 晶体管不工作,此时数据输出寄存器中的 将使得 N-MOS导通,而 1 则使该引脚为高阻抗态。推挽输出模式时,两个场效应管都工作, N-MOS 导通漏电流, P-MOS 导通灌电流。

复用功能端口模式:输出缓冲区可配置为开漏或推挽方式,并由来自外设的信号驱动。进而,激活施密特触发器,并根据 GPIOx_PUPDR 决定是否激活弱的上拉/下拉电阻。同样,每个 AHB 时钟周期该引脚的数据将被采样到输入数据寄存器,读输入数据寄存器时返回引脚状态。

6.IIC 仲裁机制

通过 SCL 上的“线与”功能,可以实现多主设备时钟的同步;

在每一个位周期,当 SCL 为高电平时,每个主设备就检查当前 SDA 上的电平与自已发送的数据是否一致,如果一致,则继续使用总线并检测;

当主设备检测到第一个不一致数据时,即发送的是高电平,但检测到 SDA 是低电平的,该设备便获知冲突发生且自己失去了总线的使用权,关闭输出驱动器,而其他主设备继续传输并检测。

IIC 总线设计系统时,需要分别为 SDA SCL 信号线接一个上拉电阻 RP ,这也意味若总线空闲时 SDA SCL 均为高电平。

7.内核

OS的核心组件,是一个可以独立运行的软件对象,与操作系统的其他组件协同工作以提供系统级服务;

提供任务管理、同步、调度及定时器、中断与异常处理、基本的内存管理等功能;

分类:

非抢先式内核

抢先式内核

微内核、超微内核架构:现代操作系统的架构,将共性核心功能与可选组件进行分离;

内核是最早被加载运行的组件,提供任务调度、任务间通信、中断/事件分发等基本、核心的系统服务,并以其为中心向外扩展软件功能;

优点:

结构灵活、关键代码分区存放、防止非法访问;

微内核OS较单内核OS具有核心更小、组件化程度高、使用更灵活

EOS采用微内核结构:

基于微内核或超微内核(Nanokernel),内核缩小至几十KB甚至几KB;

高度组件化,提升可配置、可裁剪能力;

单核处理器上的超微内核是一个事件分发器,能够最先捕获系统中产生的中断和事件,进而将其分发给上层的系统内核或应用;多核处理器上,超微内核根据需要分配处理器核资源。

超微内核:规模最小,OS最核心,主要完成中断、事件的分发,部分还可以对多核处理器资源进行分配;

微内核:基于超微内核的扩展,具有任务调度等功能;

内核:一般指增加了任务间同步能力的微内核;

执行体:则是包括了私有内存块、I/O服务以及其他复杂机制的微内核,大多数商业嵌入式实时操作系统都属于该形式;

操作系统:通常指提供了用户交互接口、文件系统、数据库、安全服务等组件的执行体,是一个完整的系统软件。

8.任务优先级

表示任务紧急程度的重要属性;

是嵌入式操作系统内核进行任务、中断管理的重要依据之一;

抢先式内核中,任务的优先级越高,表示该任务应该越早地被调度执行;

最低优先级的中断程序也要比最高优先级的任务优先执行。

通常情况下,优先级的值越小,表示优先级越高,不同嵌入式操作系统中对任务优先级的约定不同;

9.共享资源与临界资源

共享访问

临界:一次仅允许一个任务访问

10.优先级翻转

理想地,基于优先级的抢先式调度策略:在任何时刻都应保证高优先级的任务优先执行;

实际上,常常会出现“因为低优先级任务持有高优先级任务所需的临界资源,从而导致高优先级任务被延迟执行”的现象,即优先级翻转问题(Priority Inversion);

12.优先级继承协议

解决优先级翻转问题

Priority Inheritance Protocol, PIP

核心思想:优先级翻转问题发生时,让持有共享资源的低优先级任务获取被阻塞高优先级任务的优先级,以尽快执行并释放共享资源,进而使高优先级任务能够得到快速响应。

比较

优先级继承

仅在发生翻转式更改优先级

可能会多次比较和更改优先级

T1持有资源S0,运行;

T2(P2>P1)到来,中断T1;

T3(P3>P2)到来,中断T2,申请资源S0;

优先级翻转,P1提升到P3,T1执行;

T4(P4>P3)到来,申请资源S0;

优先级翻转,提升P1至P4,T1执行;

优先级天花板

不论是否发生优先级翻转,只要任务访问共享资源都会提升任务的优先级;

简单,但浪费很多CPU时间,影响实时性。

13.任务间通信

共享内存区域:

在公共内存区间,创建可由多个任务共同访问的存储空间并创立相应的数据结构,可以实现多任务间的数据交换。

多个任务要进行写操作时,必须对区域进行互斥保护。

可采用更为复杂的、可容纳更多数值的共享数组(线性缓冲区)、循环数组(环形缓冲区)、链表、指针变量等数据结构。

任务之间,或处理机之间(如VME总线的共享内存区间)。

消息队列:

内核中为多任务交互提供的以消息为单元的数据交互机制。

内核可以同时创建、维护多个消息队列。

每个队列有其独立的ID,队列中的消息数量和长度可变。

考虑任务的优先级因素,嵌入式操作系统内核一般都会支持传统FIFO队列和优先级消息队列机制。

缺陷

队列、信箱、管道可以为共享数据提供方便,但也容易出现系统错误;

队列等的空间已满对于嵌入式软件来说是灾难性的,要保证其拥有足够空间;

通过队列等机制传递指针可能引起共享数据问题;

14.事件与事件组

事件是基于同步模型的多任务之间、任务与中断服务程序之间、任务与操作系统资源之间的通信机制;

支持事件机制的操作系统内核中,每个任务的TCB中会包括一个二进制的事件寄存器,寄存器的每一位对应一个事件二进制事件标志(Event flag);

允许多个任务阻塞在同一个事件上当事件到来时,内核将依据任务的优先级从阻塞在该事件的任务队列中选择并释放一个任务;

允许一个任务等待在“与”或“或”逻辑的事件组上;

当一个事件解除了一个等待的任务后,一定要对该事件的值进行重置(清除、复位);

内核复位、代码复位

第一章 概述

1.1 分析计算机、网络的发展过程,简要阐述嵌入式计算系统的出现与发展历程。

随着电子器件技术的不断发展和演化,基于半导体材料的晶体管技术、集成电路技术出现,计算机硬件的体积、功耗降低,处理速度提升才能使专用的微型计算装置“嵌入”到应用对象中;C语言等软件语言的出现支持系统功能复杂化;网络通信技术促进嵌入式系统的发展。

1.2 在嵌入式系统发展史上,三次重要的技术飞跃分别是什么?其各自对于嵌入式系统的发展有何促进?

第一次飞跃是集成电路技术的诞生促进嵌入式微处理器的出现,使得硬件可以“嵌入”;第二次飞跃是C语言的出现可以支持复杂功能;第三次飞跃是嵌入式操作系统的出现 使得功能更丰富。

1.3 辨析嵌入式系统的概念,进而分析其典型组成结构与特点。

嵌入式系统:如果一台计算机(及其软件)是一个大系统中集成的一部分,并且通过特定的硬件装置来控制和/或直接监控该系统,其就被认为是嵌入式的。即首先应该满 足的条件是大系统中集成的一部分,其次是通过硬件装置对外界进行感知和做出相应的反应。

组成结构为嵌入式硬件、嵌入式操作系统与服务以及嵌入式应用软件;嵌入式硬件是整个系统的载体,以嵌入式处理器为核心;嵌入式操作系统是管理嵌入式硬件资源并进 行服务能力扩展的系统级软件,即提供可定制能力和性能保证;嵌入式软件是面向特定应用所开发的软件系统。

特点:专用性强、资源定制化、多元的非功能属性约束、资源相对受限、一体化硬件设计、技术途径丰富、知识与技术密集。

1.4 如何理解嵌入式计箕无所不在,同时又日益“消失“在物理世界中?

一方面,随着嵌入式计算的发展,其装置可以嵌入到越来越多的各式应用中,同时嵌入式与大数据、云计算等新型计算模式不断融合,因此称嵌入式计算无处不在。

另一方面,由于网络通信技术的发展以及不断丰富的感知与作动能力和提高的集成度,嵌入式系统可以深度嵌入到越来越多的物理对象中,促进信息系统与物理世界的日益融合, 因此可以说嵌入式系统日益“消失”在物理世界中。

1.5 要设计移动电话软硬件系统,可能需要设计者具备什么样的知识体系?什么样的移动电话可以算作是智能的?

需要具备的知识体系有组成原理与系统结构、数字电路及硬件设计、计算机接口技术、操作系统、数据库技术以及编程语言与软件工程,即需要多领域的、软硬件结合的知识体系。

智能的应该是能够与人进行自然的人机交互,并且能够通过外界的反馈信息自主对其内部系统进行调节。

第二章 嵌入式硬件基础

2.1 分析、比较 TTL 电平、 CMOS 电平和 RS-232 电平的特点。

TTL电平(电流控制器件,+5V等价于逻辑1,0V等价于逻辑0):输入时,高电平>2.0V,低电平<1.2V;输出时,高电平>2.4V,低电平<0.8V。

CMOS电平(采用12V电源电压):输入时,高电平>8.4V,低电平<3.6V;输出时,高电平>10.8V,低电平<1.2V。

RS-232电平(负逻辑电平):-3-12V为逻辑1,+3+12V为逻辑0。

2.2 阐述电路中上/下拉电阻的用途和基本工作原理。 !!!

上下拉电阻用于防止部分的信号浮动情况。

上拉电阻是指连接在元件信号引脚和高电压之间的电阻,用于将引脚信号钳位在高电平,或者用来在驱动能力不足时提供电流。

下拉电阻是指连接在元件信号引脚和GND之间的电阻,用于将信号钳位在低电平,或者用于吸收电流。

2.3 简述漏极开路、推挽电路的工作原理,并解释为何多个漏极开路器件的输出可以进行“线与“连接而多个推挽电路则不行。 !!!

漏极开路由于漏极浮空,因此场效应管只能在I/O向栅极供电时导通并“漏”电流(吸收电流),输出低电平。所以,开漏电路也可以支持多个开漏输出引脚的有上拉电阻限流 的“线与”连接。

推勉电路在输出端采用了两个互补的三极管或MOSFET,顶部是P-MOS场效应管,地卜师N-MOS场效应管。当顶部晶体管导通,底部晶体管关闭时,顶部晶体管导通接高 电压,输出高电平;反之,顶部晶体管关闭,底部晶体管导通时,底部晶体管接地,输出低电平。由于将两个或多个推勉电路连接在一起时,一端输出为高电平(灌电流) 而另一端为低电流(漏电流)时,将在两个引脚之间产生瞬时的大电流,引发总线竞争问题并可能造成电路损坏。

2.4 旁路电容、退耦电容的作用是什么?应如何布放? !!!

退耦电容主要起到消除电路之间的寄生耦合、滤除输出信号的干扰和缓冲电荷的作用;应该布放在靠近相应引脚(电源或信号)的地方,电容的电源或信号走线与地线所包 围的面积最小。

旁路电容也起到滤波、抗干扰的作用,其主要工作原理是将输入信号中的高频噪声作为滤除对象,将前级携带的高频杂波滤除。布放在输入信号引脚附近。

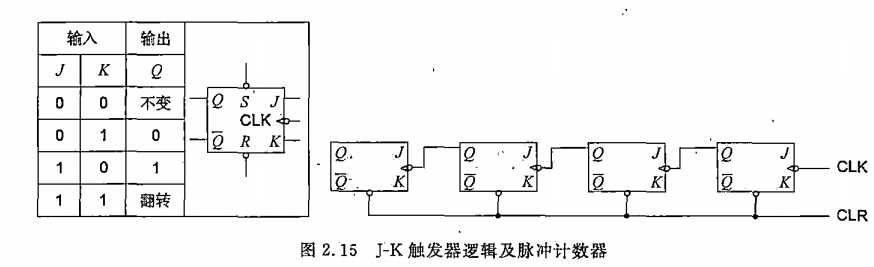

2.5 分析图 2.15 脉冲计数器的计数过程。

即每次时钟周期进行一次翻转时,都会使四个触发器的数位有翻转或者保持;第一个周期到来时,第一个触发器产生数位1;第二个周期到达 时,第一个触发器发生翻转为0,第二个触发器产生数位1;以此类推。

2.6 简要阐述嵌入式硬件子系统的组成及其功能。

处理器子系统:是嵌入式计算装置的核心,连接各种外设进行工作。

存储子系统:是计算装置必不可少的功能组件,用于存储程序和数据,有助于提高指令和数据的访问效率。

时钟子系统:为计算系统的运行提供时钟控制脉冲信号,是处理器、存储器、总线以及WDT、UART等I/O有序、正常工作的重要条件。

I/O子系统:是围绕嵌入式处理器扩展出的接口子系统,采用内部总线、板级总线和接口电路连接大容量存储组件和用于交互的I/O组件,用于计算装置与外界设备、操作人 员的数据通信和用户交互。

外围电路:用于连接、激活甚至是监控,以使得嵌入式硬件的逻辑运行正确且可靠。

调试子系统:用于调试嵌入式系统的软硬件资源总成。

2.7 嵌人式系统的硬件形式有哪几种?各有什么特点?

基于通用计算机扩展的嵌入式硬件:其硬件主要采用了“通用计算机+I/O扩展+特殊外围”的架构,重点是对通用计算机硬件进行I/O接口与组件的扩展。

基于领域标准模块集成的嵌入式硬件:以通用或嵌入式处理器为核心设计的单板计算机,集成尽可能完整的领域型功能模块和接口,具有良好的机械、电气性能和可扩展 性,可以支持嵌入式系统硬件的快速构建。

针对具体应用设计的嵌入式硬件:构建专门的嵌入式计算机,以减少资源浪费和生产成本

2.8 降低嵌入式系统硬件功耗的方式有哪几种?

低功耗器件设计:采用具有动态调节能力的双电源电压机制;增加控制电路休眠的门控电源逻辑,可以让电路某部分长时间断电;根据系统性能需求将时钟动态调整至适当频率,从而降低功耗。

低功耗系统设计:选用低功耗的电子元件和外围器件;选用集成度高的电子元件并充分利用元件内部继承的功能单元;通过寄存器关闭不需要的外设控制器;采用低功耗接 口电路。

2.9 简述基于 EDA 软件的硬件电路设计基本流程。

电路原理图设计:在元件库中找到相应元件的符号,进而定义、绘制电路,连接形成原理图文件。

定义元件封装:对所有电子元件的封装进行正确设置。 PCB参数设定:设置PCB板及过孔、导线等的物理参数。

生成、加载网络表:Protel可自动生成网络表并检查网络表是否存在错误。网络表是描述电路元件及其参数、线路连接关系等信息的文档文件,是电路原理图和印制电路板设计的接口。

元件布局:按照高低频、高低压以及隔离、散热等特性进行合理调整。 布线规则设置与自动布线:设置后可通过软件自动布线。

手动布线:由于元件布局、电磁兼容或版面设计等因素,需要手动布线加以调整或优化。

电气规则校验:使用软件的校验功能来验证所设计PCB的可行性。

打印、制板:将PCB打印在胶片上形成制板底片,之后依次通过曝光、显影、蚀刻等流程的处理形成PCB电路板。

第三章 嵌入式处理器

3.1 简述处理器微架构的含义,给出一个处理器微架构的描述。

微架构又称为微体系结构/微处理器体系结构,指将一种给定的指令集架构在处理器中执行的方法。一种给定的指令集可以在不同的微架构中执行。

3.2 什么是微控制器?请描述其基本逻辑组成及特点。

微控制器是一种快速构建微型计算装置电路所必需的控制单元。

普遍以CPU为核心,在片内通过内部总线连接,集成了必要的程序/数据存储器、定时器/计数器、中断控制 器以及特定I/O接口与组件,进而为嵌入式控制系统设计提供一个较为完整的计算系统核心。

特点是:计算核的指令数较少、位处理指令较丰富、供电电压较单一、计算性能通常不高、组件集成度较高、提供多种O/I接口、引脚数量相对较少、低功耗、低成本、使用方便,以及适合简单控制系统等。

3.3 ARM 指令集、 Thumb 指令集各有什么特点?为什么 Thumb 代码并不总是比 ARM代码高效?

ARM指令集可分为六大类,几乎所有的ARM指令都有4位的条件域,为32位指令集。

Thumb指令集是基于ARM指令集进行重新编码的子集,指令长度固定为16位。与ARM指令集相比,在功能和性能上进行了一定限制,Thumb指令集是为了提升使用16位或更窄内存总线的ARM处理器的性能,并提供较ARM指令集更为优化的代码密度。

在使用32位存储器的时候,ARM指令集更快,原因是Thumb是针对16位进行的改良。

3.4 比较 ARM 体系中 A32 T32 A64 指令集的特点。

A32表示支持32位ARM指令集;

T32表示支持32位ARM指令集和16位Thumb指令集;支持用户代码更好的代码密度,为编译器提供了优势,有机会在单个指令集中平衡性能和代码大小权衡。

A64表示支持32位指令集,特点有:基于5位寄存器描述符的简洁解码表、指令语义与A32大致相同、31个随时可供访问的通用64位寄存器、无模式通用寄存器组、非通用的 PC和SP以及可用于大多数指令的专用零寄存器(2R)。

3.5 CPSR SPSR 寄存器的功能是什么?何时使用 SPSR?

CPSR是保留所有处理器状态的状态寄存器,模式M表示处理器工作模式;除了用户模式之外,其他6种模式有独立的处理器状态保存寄存器SPSR。

3.6 ARMv7-M 中引入了哪些新的寄存器?各有什么作用和特点。

有两个堆栈指针寄存器SP_main和SP_process(是R13的分组模式);

专用的32位程序状态寄存器xPSR(分为应用程序专用状态处理器ASPR、中断程序状态处理器IPSR和质 心程序状态寄存器EPSR);

3个管理异常和中断优先级的32位掩码寄存器MR;

一个32位的控制寄存器CONTROL,用于设定当前堆栈和线程模式的权限级别。

3.7 ARM 32 位指令集编码中,条件码字段的作用是什么?

一共有16个值,一个值用于指定指令无条件执行,14个值指定指令的执行条件,第16个值用于可选指令的编码。

3.8 简述异常和中断的内涵及其关系。

异常模式是指正常运行的用户程序因为某些事件被暂时中止,导致进入的特定处理模式。即进入异常模式后,主要靠中断进行异常处理并返回到正常程序中继续运行。

3.9 分析、对比 ARM MIPS PowerPC 体系架构的特点。

ARM架构:是一种32位精简指令及处理器架构,具有RISC体系的基本特征,包括:一个大容量的、统一的寄存器文件;采用加载/存储模式,在寄存器中而不是内存中进行 数据处理;仅从寄存器及指令中读取地址,寻址简单;采用一种指令长度,简化指令的解码过程。 MIPS架构:是一种简单的流水型、高度可扩展32位、64位RISC架构。特点包括:高性能、行业标准的体系结构;固定长度、统一编码的指令集,所有指令集都向后兼容; 采用加载/存储数据模型,所有操作都在寄存器上进行;开放式架构,允许用户在开发的内核中自定义指令;具有32位/64位两种架构的指令集;计算核内包括大量寄存器、 指令数和字符;具有并行流水、超级流水以及多通道超标量流水等流水线结构,流水线延迟间隙可视;集成度高,芯片面积更小,功耗高于ARM;采用多发射核技术,用处 理器中的闲置处理资源虚拟另外一个计算核,提高处理资源的利用率。 PowerPC架构:是一种典型的高性能RISC处理器架构,其特点为:可实现单核/多内核架构;采用多发射、分支预测的超标量流水线结构,并行度高;丰富、独立的整型寄存 器组和浮点寄存器组,支持32位/64位计算和访问;采用统一定长的精简指令格式,最多可支持4个操作数;高效的分支处理;内存访问基于内存与GPR/FPR间的加载和存储 指令完成;为GPR和FPR之间的数据传输提供专门指令;突出的浮点性能,提供支持IEEE 754标准浮点数的运算指令;良好的伸缩性,可根据特定需求进行架构扩充;应用 范围广。

第四章 嵌入式存储技术

4.1 为什么计算系统需要采用多级的存储体系?

基于不同类型数据存储、访问的要求差异,以及数据访问在时间、空间和顺序上的局部性原理,计算系统的存储子系统主要采用了分级的存储体系。

4.2 为什么 DRAM 中不采用独立的行、列两组地址线,而是复用同一组地址线?

使用同一组地址线进行分时传输,可以减少芯片引脚的数量。

4.3 CPU 访问 DRAM 会产生延迟,如何优化和解决?

为了使DRAM有效地存储信息,必须定期为已充电的电容补充电量,即进行DRAM的刷新操作,在刷新期间DRAM控制器会向CPU发出DRAM忙的信号,CPU的读写请求将 会被延迟。

可以采用快速页模式(触发行地址后,CPU连续输出多个列地址来访问不同的位)、扩展数据输出(无需等待此次访问是否完成,只要达到规定的地址有效时间就开始输出 下一个地址)、同步DRAM(采取了与CPU外频同步的DRAM频率,消除了访问冲突引起的CPU等待周期)等方式进行优化和解决。

4.4 简述 LPDDR SDRAM 的特点。为什么该类存储器适合移动嵌入式系统?

LDPPR是面向智能手机、平板电脑等嵌入式系统的SDRAM产品,具有体积小、功耗低、更高的频率,因此更适合作为移动嵌入芯片。

4.5 简述双端口 RAM 的架构特点,并分析同时进行读写操作时的互斥机制。

架构特点为拥有两套独立的数据线、地址线和读写控制线,是两个CPU之间进行快速传输块数据的有效方式。

其互斥机制主要通过三种方式实现:

1)中断方式,当左CPU 写特定的信令地址时,信令交换逻辑向右侧CPU发送中断,通知其开始数据访问操作;

2)忙逻辑方式:当两个CPU同时访问存储器时,仲裁逻辑会选择出一个CPU进行授 权,并通置BUSY引脚将忙状态通知给另一个CPU;

3)信号量方式:提供硬件信号量仲裁机制,控制软件访问、获取硬件信号量SEM实现对存储单元的互斥访问。

4.6 分析 EEPROM Flash 访问过程与性能的异同,并从微电路和结构角度阐述原因。

EEPROM采用浮栅管单元技术,通过电进行擦除,访问时是通负电荷写入来实现数据位的写入,读取时通过判断浮栅中有无电子进一步电路是否导通来判断0或1,访问速度较快;

Flash同样采用了浮栅管单元技术,其擦除机制是基于隧道效应的编程与擦除机制,与EEPROM类似;访问时通过存储元的源、漏极是否导通来表示0和1,读取快,写入较慢。

原因是Flash中采用的是新型隧道氧化层MOS管,该晶体管的隧道层在源层且更薄,允许在控制栅和与源极之间加12V电压就使隧道导通。同时,Flash芯片内集成了高压产生 电路(高压泵),因此可以在单电压供电输入的基础上,面向不同操作特性来提供不同的工作的电压。

4.7 分析 NOR Flash NAND Flash 的架构和访间特性,说明为什么 NOR Flash 适合存放代码,而 NAND Flash 适合存放大块数据。

NOR Flash有对的地址线和数据线,按照字节读取,读取和传输速度快;以区块的方式擦除并以字节方式写入,擦除和写入速度较慢,因此适合存储小容量数据存储如代码。

而NAND Flash具有更高的存储密度,更快的写入速度,耕地的价格以及更好的擦写耐用性等优点,要修改时必须重写整个数据块,适合存放大量数据如大块数据。

4.8 为什么对 Flash 存储器单元进行写操作之前必须先对其进行擦除操作?

在写入0的时候,需要同时对栅极和漏极加上高电压,源、漏极之间的电子就会进入浮栅。Flash擦除是写1的过程,编程的时候只对非0位进行注入电荷操作,即只写入0.

4.9 简述铁电存储器中存储元的结构、物理特性及其存储机制。

存储元的结构是“两个晶体管+两个电容”的2T2C结构,每个存储元包括了数据位和各自的参考位;2001年后采用更先进的1T1C结构,所有数据位使用相同的参考位。

其物理特性是既有RAM的随机访问特性又非易失的特点。

其存储机制主要是通过铁元素的词性和原子运动过程实现的,利用了铁电晶体材料的铁电性和铁电效应。通过将充电波形 与参考位的充电波形比较,根据有无尖峰即可判断存储元中的原子位置状态,即数据位的值。

4.10 简述 BBSRAM 的工作机制及其优缺点。

BBSRAM即内带电池保护的SRAM,其结构为SRAM+锂电池+监控保护电路。优点是实现方便、成本较低,应用于诸如主板上的BIOS配置信息存储。缺点是设计中需要考虑 额外的电源管理电路和固件,需要更换失效的电池,削弱了系统的可靠性,并且体积较大。

4.11 测试 ROM 数据的方法有哪几种?简述其原理。

校验和方式:编程前计算数据的校验和,并将数据及校验和编程到只读存储器;系统启动时从存储器读出数据以及校验和,用同样的方法计算数据的校验和并与读出的校验和进行比较,如果相同则正确。 循环冗余码校验:将信息多项式与生成多项式进行模2除法运算,计算出的数据CRC校验结果存放在特定存储区域。

纠错码方式:以海鸣威码为例,海鸣威码是一次只能纠正1位错误的冗余编码,若码距为n,则最多可以检测数n-1位数据错误,最多只能纠正小于 [(2)^(-1)]n 位的错误。

4.12 CRC 校验中,定义的生成多项式为 G(X)=X’+X’+X+l ,信息码为 10110010,请计算 CRC 检错码。

首先将10110010左移6位,形成的扩展信息码为10110010000000; 采用模2除法,用10110010000000除以生成码1100011; 得到校验码0000111。

第五章 最小系统外围电路设计

5.1 简述复位的原理和目的,比较上电复位、看门狗复位、软件复位的异同。 !!!

复位是在系统电源建立的时候,为cpu或某些接口电路提供一个几十毫秒甚至数百毫秒的高或低的复位脉冲(原理),利用这段时间,系统振荡器启动启动并稳定下来,cpu 复位内部寄存器及指针,为程序启动做准备(目的)。

上电复位的原理是电源电压达到可以正常工作的阈值后,集成电路内部的状态机便开始初始化器件,使得芯片在上电后一段时间内进入已知状态,并在完成初始化之前忽略 除引脚之外(如有)的任何外部信号。

阻容式复位电路的原理是利用电容两端电压的指数变化特性为芯片的复位引脚提供复位信号。

软件复位是指通过软件指令或者对寄存器的修改触发芯片的复位脉冲,进而使系统初始化硬件并重新加载、运行嵌入式软件。

三者的原理各不相同,其相似点是都是发出复位信号,使得必要的寄存器、I/O接口等资源的值和状态能够初始化。

5.2 分析正弦波振荡电路基本组成及各组成部分的功能。

正弦波振荡电路一般由放大电路和正反馈网络组成正弦波生成电路(电路自激振荡机制)。在电源接通瞬间,电冲击、电干扰、晶体管的热噪声以及人体干扰等产生噪声信 号,在“电干扰-放大-选频-正反馈-放大-选频-正反馈…”的过程中,频率未被选中的信号不断被抑制,而选中信号不断被加强,再结合晶体管的线性区放大特性,输出和反馈的振幅稳定下来,振荡过程建立。其中,放大电路起增大输出幅值的作用,反馈网络约束相位平衡,稳幅电路稳定输出信号的幅值。

5.3 分析 STM32 LO 嵌入式处理器的低功耗模式原理、特点以及进人与唤醒方式。

其低功耗模式原理主要是降低V_CORE电压值、降低CPU频率和性能并限制启用的外设数量。其特点是仅当V_CORE在区间2时可以进入该模式;系统时钟的频率不超过 f_MSI区间1限制启用的外设数量;所有的I/O引脚保持运行模式时的状态。唤醒方式是调压器被设置为主模式(1.8V),无唤醒延迟。

5.4 降低处理器功耗的主要方法有哪些?简述各种方式的原理和特点。

对电源电压的动态调整,根据功率与电压平方之间的反比关系,降低系统动态功耗可以采用降低供应电压方式进行调节;

开启/关闭部分组件,由于开启的组件数量更多,需要消耗的功率越大,因此通过开启/关闭部分组件能够减少相应的功耗。进一步可以使电子器件运行于不同的模式,较为灵活多变;

降低器件的频率,由于频率越高功耗越大,可以通过降低器件的频率减少器件的功耗,一般由制作工艺决定。

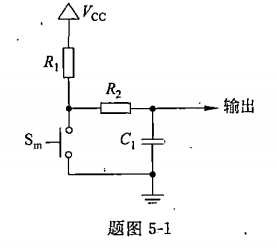

5.5 分析开关电路抖动产生的原因以及题如题图 5-1 所示电路中的消抖过程。说明电阻 R2 在这个电路中的作用。 !!!

由于电子设备中开关引脚的断开与接通可能会产生多个信号,或者由于电磁干扰会在信号线上耦合出本不应该出现的毛刺信号,这类现象称为“抖动”。

在题图中,C1电容起到消抖过程中的重要作用。上电后,C1经充电拉升至高电平。当开关闭合时,电阻R2的一端接地,C1放电一段时间后,输出为低电平。故Sm开关闭合 瞬间产生的信号被RC电路补偿和抵消,从而产生稳定的信号。

电阻R2在这个电路中起到保护电路,防止电容被击穿的作用。

5.6 在题图 5-1 基础上,设计一个基于施密特触发器的开关消抖电路,并阐述其消抖原理及响应特性。

如图所示

其消抖原理是增加了一个包含了正反馈、具有迟滞现象的比较器电路,在仅输入电压发生足够的变化时输出才会改变,因此能够消除开关断开和连接时微小输入电压变化所引起的可能的电压改变。

第六章 接口、总线与网络扩展

6.1 在图 6.3(a) 的基础上设计一个主从式 SPI 总线系统,一个 SPI 主设备和 个从设备形成位长为 (n+l)X8 的循环移位寄存器。请给出硬件原理图,并分析数据传输过程。

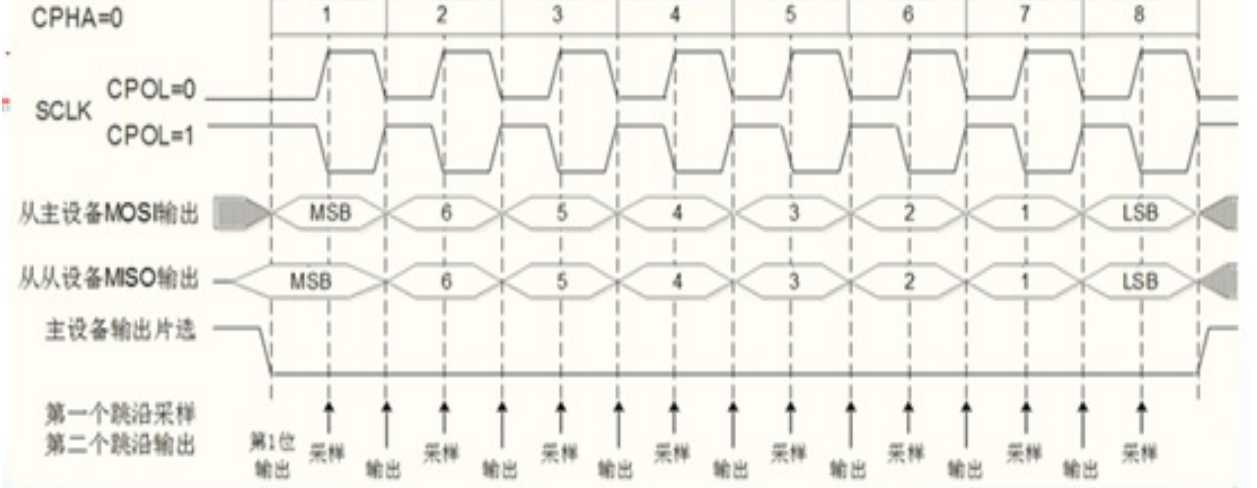

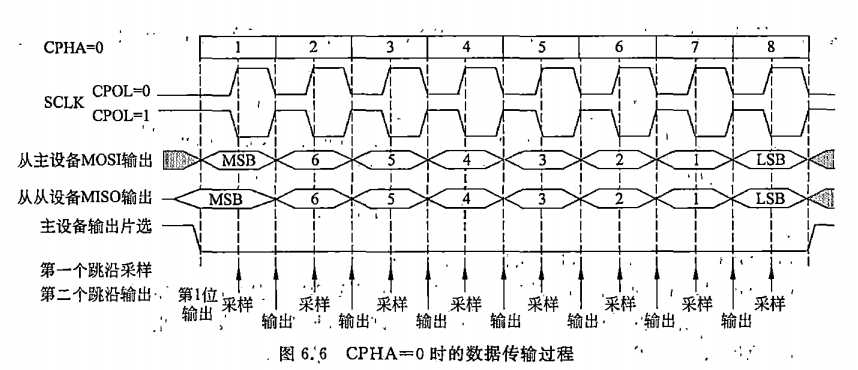

6.2 参照图 6.6 ,画出 CPHA=l SPI 各引脚的信号时序图,并与图 6.6 对比采样和数据输出的时机有何差异。

如图所示,可以看出CPHA=1时,表示第一个跳沿输出,第二个跳沿采样;因此在CPOL=0时即正脉冲时,在下降沿进行采样,在上升沿进行数据的输出,数据第一位和其 他位输出时机也在上升沿;CPOL=1时即负脉冲的时候,在上升沿进行采样,在下降沿进行数据的输出。

与CPHA=0时进行对比,可以看出CPHA=0时,表示第一个沿采样,第二个沿输出。因此在CPOL=0时,在上升沿进行采样,且在上升沿之前数据已经准备好,在下降沿进行 数据的输出。

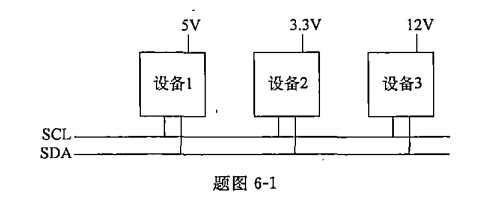

6.3 题图 6-1 所示是基千 FC 总线设计的三设备连接系统,请问该设计有何问题,如何解决。

由于I²C电路总线和设备需要支持多设备共享同一信号线的“线与”能力,因此SCL和SDA的接口内部逻辑只能采用“开漏”或集电极开路模式,因此需要分别为SDA、SCL信号

线接一个上拉电阻Rp。

6.4 为什么说 I2C 总线的仲裁过程中并不会丢失任何数据。

通过SCL上的“线与”功能,实现多主设备时钟的同步;在每一个位周期时,当SCL为高电平时,主设备检查当前SDA上的电平与自己是否一致,如果一致则继续使用总线并

检测;如果不是则该设备获知冲突发生且自己失去了总线的使用权,关闭输出驱动器,而其他主设备继续传输并进行检测。I²C规范通过这样的冲突检测和仲裁I²C解决多个

主设备竞争总线时的冲突和破坏问题,即保证仲裁过程中不会丢失任何数据。

6.5 实际设计中,影响 UART 数据传输速率的因素有哪些?有哪些解决方法?

将UART传输速率使用波特率进行衡量,则有以下几个因素。

缓冲区FIFO的大小。如果接收缓冲区过小,其数据在读取中就会被后续字节覆盖进而产生错误。

通信距离。信号在介质中传播时其自身能量会不断衰减,抗干扰能力变弱。为了使信号有足够的能量会采取加大信号宽度这一措施,而信号宽度增加后单位时间内可传输的信号数量减少,即波特率降低。

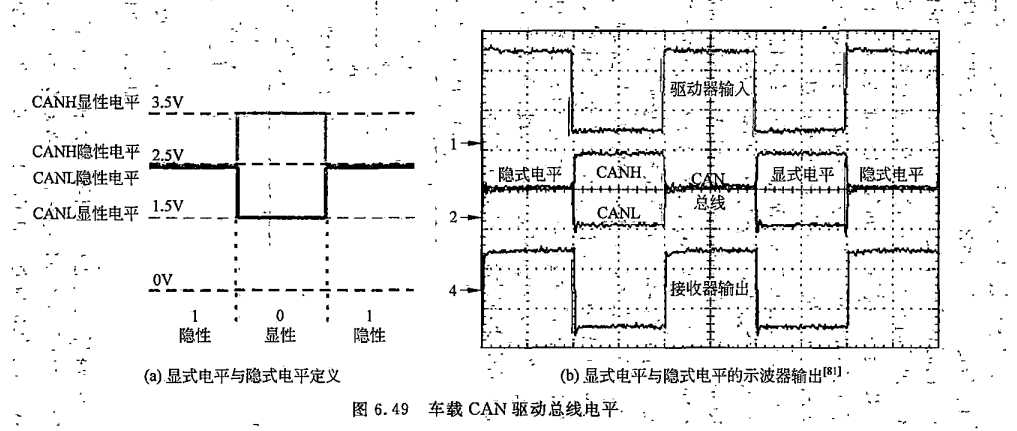

6.6 分析车载舒适总线中的电平状态,并参照图 6.49 画出 CANH CANL 的变化关系。

隐性状态时,CANH和CANL(两条差分线路)分别为预先设定的电压值,如车载CAN驱动总线中都为2.5V,而车载舒适总线中CANH为0V、CANL

为5V,V_CANH-V_CANL为0V或者-5V,表示“1”。在显性状态时,CANH上的电压升高一个预定值,则CANL上的电压值会降低一个同样的值。某一时刻,总线电平要么处

于显性水平要么为隐性水平。

6.7 IrDA 和蓝牙技术都用千短距离无线通信,请比较二者的特性有何异同点。

不同点:

1)IrDA使用红外线作为通信媒介,是点对点传输;蓝牙指无线数据和语音通信的短距离无线通信技术标准,支持点到点、点到多点。

2)特征上的差异:具有相同红外接口的设备之间可以进行信息交换,安全性较强,传输距离短;蓝牙将内嵌蓝牙芯片的设备互联起来,提供语音和数据接入服务,易于组网。

相同点:其系统架构基本相同,基带芯片和射频单元组成一个模块运行底层的物理层和链路层的功能;高层协议由单独的CPU运行。均应用于家庭和小型办公室的应用场

合,是主要的PAN技术。

6.8 一个蓝牙设备组成的微微网中,在什么状态下可以有多于 个的从设备?该从设备状态有什么特点和用处?

在等待状态下,设备的活跃成员地址AM_ADDR修改为PM_ADDR,此时其所在微微网的就可以存在多余7个从设备。在该设备状态下,设备的活动非常少,从设备不必加入微微网,但仍保持为微微网成员,其用处是功耗降低。

6.9 分析、对比 Bluetooth ZigBee Wi-Fi 技术原理与特点。

6.10 简述 WiGig 的原理和特点,并将其与 Wi-Fi 技术进行比较。

Wigig为第五代标准IEEE 802.11ad,称为千兆无线局域网,其主要是通过60GHz频谱进行数据传输,可以保证在各种情况下实现更稳定的传输,能够在最大10米的距离内提供 大约5Gbps的无线网络速度。其与Wi-Fi比较传输速度更快,但传播范围更小。

6.11 设计 ZigBee Bluetooth Wi-Fi 接口的方式都有哪几类?分别有什么优缺点?

Bluetooth接口可采用USB、UART等,只需要通过这些接口发送操作命令就能够实现对蓝牙通信。 ZigBee使用的是GPIO接口,输出功率较低,有效通信距离不够。

第七章 嵌入式软件结构与基础软件

7.1 结合 ARM 处理器特性,分析裸机软件和嵌入式操作系统的启动过程。

由于裸机软件直接在硬件上部署和运行,因此其启动过程较为简单,只需要将编译生成的二进制代码烧写到 NANDFlash 的 0x00000000 地址。系统复位后,处理器上电复位; NAND 控制器将 NANDFlash 中的启动代码赋值到 ARM 的 SRAM 中;处理器根据 PC 值从 SRAM 的首地址开始执行即可完成启动过程。 对于嵌入式操作系统而言,在上电启动后,还需要将 Boot Loader 代码从 Flash 复制到 SDRAM 的特定区间并引导执行。Boot Loader 首先执行一系列基本的硬件初始化工作,然后为操作系统运行做好环境准备,并将外部存储器中的操作系统内核映像复制到内存中的代码和数据空间,设置内核启动参数。最后跳转至内核入口地址开始执行。至此,嵌入式操作系统的启动才全部完成。

7.2 简述 ROM Monitor 软件的工作原理及其在嵌入式系统开发中的作用。

ROMMonitor 软件的工作原理是上电后,ROMMonitor 对硬件进行基本的初始化,进而可以通过串口/网口与开发主机交互,执行程序加载、命令执行、程序调试等操作,并 提供一个简单的用户命令接口、支持对程序设置断点并单步跟踪及集成调试器,使开发人员能够在嵌入式系统开发过程中对资源进行管理并进行软件调试。

7.3 Boot Loader 的最小功能是什么?与 BIOS 有何异同?

Boot Loader 的最小功能是至少应该驱动一个外部的数据通信接口,且提供一种读、写、擦除 Flash 的方法。Boot Loader 与 BIOS 的相似点在于功能,都能完成对于处理器相关的 硬件资源进行初始化、内存映射建立、代码搬移与启动等操作。 区别在于: Boot Loader 是嵌入式系统组件,与具体硬件平台密切相关,需要面向硬件平台定制;设计人员需要关注 Boot Loader 的功能和机制。 BIOS 负责初始化硬件,之后调用操作系统加载代码,而 Boot Loader 包含了全部这些功能; 通用计算机中一定存在 BIOS ,而嵌入式硬件中可能不存在 Boot Loader ; BIOS 一般不能更改, Boot Loader 允许配置或增加新的功能; BIOS 通常是主板上独立的 ROM 单元,Boot Loader 可以是独立 ROM ,也可以和操作系统、应用代码共同存储在 Flash 的不同区域; 系统启动后 BIOS 的运行时服务驻留在内存中,目标操作系统及应用仍可使用。而 Boot Loader 完成引导任务后不再有效,成为哑代码。

7.4 BSP 包具有开放性,允许设计人员将自己的应用代码添加到 BSP 中,这种做法是否可取?为什么?

BSP(板级支持包)是位于嵌入式系统硬件和嵌入式操作系统之间的软件包,形式由嵌入式操作系统决定,具体内容由硬件平台决定。由于嵌入式系统操作系统丰富多样、 嵌入式处理器不同应用系统的硬件资源类型、数量等存在差异,因此为了更好使用嵌入式操作系统,会允许设计人员将自己的应用代码添加到 BSP 中。我个人认为这是可取 的,面对多种多样的嵌入式软硬件,确实需要设计人员量体裁衣,选择最合适的 BSP 资源并进行特定BSP的开发。

7.5 分析 0型、 I型、II 型虚拟机的特点,分析为什么 II 型不适合于嵌入式系统设计。

0型虚拟机指嵌入式系统的虚拟化,即嵌入式系统部署裸机上直接运行的虚拟机监控程序,监控程序向下屏蔽和管理硬件,向上提供多个虚拟的硬件平台。 Ⅰ型是可以直接安装、运行于硬件平台的虚拟机,无需宿主操作系统,其监控程序是一种特殊的操作系统,创建一个底层硬件平台的 抽象。 Ⅱ型是运行于主操作系统之上的虚拟机,算作操作系统中的应用程序。在虚拟机上,用户可以安装客户操作系统、应用程序,与主操作系统环境同时运行。 由于Ⅱ型虚拟机是运行于主操作系统上的虚拟机,即需要宿主操作系统,不满足嵌入式虚拟机中的体积约束(其监控程序可达千兆字节)和效率约束(应具有很小的规模和 不高的内存使用率)这两个要求。

7.6 实践作业:

(1) PC 上安装 VxWorks 开发环境、 RainDiskNT 软件、VMWare 虚拟机;

(2) 创建新的工程,选择 Pentium BSP 包并配置、编译一个支持串口、以太网口的 VxW_orks 映像文件;配置生成一个从 :盘根目录加载 vxWorks 映像的 bootrom 文件;

(3) 将生成的 bootrom 复制到 RamDiskNT 虚拟的 :盘, VMWare 虚拟机从 :盘启 bootrom VxWorks;

(4) 编写实验报告。

7.7 实践作业:

(1) 安装 Windows Embedded Compact 2013 开发环境;

(2) 选择 x86 模拟器的 BSP ,配置生成一个支持蓝牙功能的操作系统内核 NK. bin;

(3) 将该映像下载到 x86 模拟器运行;

(4) 编写实验报告。

第八章 第 嵌入式操作系统及其服务机制

8.1 超微内核、微内核、内核三者在功能上有何差异和联系?

微内核仅实现基本、必要的操作系统功能,与内核相比,核心更小、组件化程度更高、使用更灵活;进一步,超微内核的功能更加单一,也更为底层。其联系是内核经过功 能裁剪后可作为微内核,微内核经过裁剪后可作为超微内核。

8.2 简述任务、进程、线程的含义,并比较其异同。

任务是指多任务编程模型中,每个并发的执行单元,是可以被调度且并发运行于处理器的软件功能单元;线程是处理器中的最小调度执行单位,进程是一组线程的资源容 器。其异同在于: 任务体现了一定的应用含义,线程、进程侧重计算的含义。 在逻辑嵌入式软件中也可能有任务的概念。 进程中的线程和任务一样有独立的上下文。

任务、线程与进程不同于函数,不能调用另一个入任务/进程/线程。

8.3 如何理解实时和实时系统?

实时是指系统能够在限定的响应时间内提供所需水平的服务。实时系统是指计算的正确性不仅取决于程序的逻辑正确性,也取决于结果产生的时间,如果系统的时间约束条 件得不到满足,将会产生系统出错。

8.4 简述硬实时与软实时的含义,并举例说明。

硬实时是指截止期是一个严格的时间约束,必须严格遵守,否则就会造成系统障碍乃至重大灾难,例如无人机控制。 软实时是指系统具有时间约束,但任务的截止期限制并不严格,例如足球赛的转播。

8.5 什么是优先级翻转问题?请给出几种解决方法,并比较这些方法的特点和异同。

优先级翻转问题:因为低优先级任务持有高优先级任务所需要的临界资源,从而导致高优先级任务被延迟执行。 解决方法有优先级继承协议和优先级天花板协议。 优先级继承协议核心思想是,优先级反转问题发生时,让持有共享资源的低优先级获取被阻塞高优先级任务的优先级,以尽快执行并释放共享资源,进而使高优先级任务得 到快速响应。 优先级天花板协议指的是为每个临界资源赋予一个较高的优先级。任务在邻接资源以外时,以原先的优先级运行;当一个任务τ尝试获取一组所需临界资源中的一个资源S 时,如果任务τ的优先级严格大于其他已被其他任务所持有邻接资源的优先级天花板,那么该任务就能获取该临界资源;否则,任务τ被阻塞,并且持有共享资源的任务继承 任务τ的优先级。 其区别在于,在优先级天花板协议中,不论是否发生优先级翻转问题,只要任务访问共享资源就睡提升其优先级,减少了复杂的判断,但是提升和恢复优先级会产生额外的 系统开销,增加对实时系统的影响。

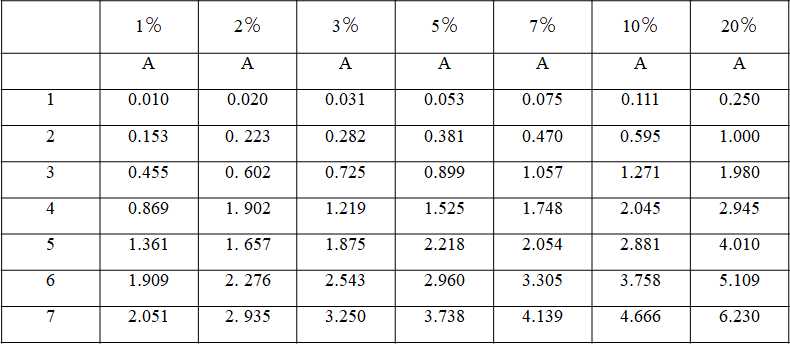

8.6 有同时到来的周期任务组: T1 -c2 、动,其(执行时间,周期)参数依次为 (ls,4s) (2s,6s) (3s,8s) ,请分析采用 RM EDF 调度算法时是否可调度?请给出两种调度算法在该任务组上的调度过程分析。

对于RM算法,U=1/4+2/6+3/8=23/24>3(2^(1/3)-1),故不可调度;

对于EDF算法,U=1/4+2/6+3/8=23/24<1,故可调度,其调度方法是以任务的截止期来设定周期任务的优先级。

其调度过程分析如下:

8.7 实践作业:

在基于 Linux 的通用计绊机上,使用 RT-Linux RTAI 对其进行实时化。进而,设计一个实时任务、一个非实时任务,输出调度序列,并验证实时任务的调度效果。

8.8 实践作业:

在 PC 上搭建 Contiki 操作系统的开发环境,开发 Contiki 应用软件并在模拟器中运行。

8.9 实践作业:

在 PC 上搭建 ROS 的开发环境,创建两个通过消息机制通信的节点,在验证节点间的通信功能后使用启动文件启动这两个节点。

8.10任务(Task)

基本概念是指“需要完成工作的一个特定部分”,强调了应用属性,是EOS中的一个软件对象;

面向无MMU的RTOS中采用了新的多任务模型

一个程序被分割为一组同级别的功能函数,如监测、通信、控制等,每个函数都类似于一个“主函数”且大都采用了无限循环;

模型中,每个并发的执行单元被称为任务,是可以被调度且并发运行于处理器的软件功能单元。

属性

任务结构(物理)

任务状态(逻辑)

8.11任务状态

反映任务当前在系统中所处的情形,由内核维护;

基本状态包括运行、就绪、阻塞、睡眠和挂起等状态;

8.12任务上下文(Task Context)及其切换

任务上下文是多任务系统中,任务被中断时所必须保存的最小数据集,涉及分配给任务的内存区域(包括堆和栈)以及处理器的寄存器组等资源。

8.13任务控制块(TCB)

进行任务管理的数据结构,包括任务上下文及任务ID、状态、指向下一个要执行任务TCB的指针、优先级等内容和属性;

内核基于TCB中的信息,将相同状态的任务挂载到相应的任务队列中进行分类管理。

8.14任务调度器(Scheduler)

是内核中以就绪队列为操作对象的任务管理组件;

以特定的调度策略从就绪队列中选取要执行的任务,进而在内核态切换任务的上下文并跳转至该任务PC寄存器所指的位置系统运行期间无限地实现任务调度管理;

第九章 嵌入式软件组件

不考,懒得写了

第十章 嵌入式应用软件设计方法

只考 10.1-10.3

10.1 请分析前后台软件结构是否提供优先级服务能力

10.2 简述中断程序设计的原则,请举例分析

10.3 什么事数据共享问题?请给出至少一种解决方法并进行分析

10.4 结合看门狗电路原理,设计“与逻辑”的看门狗任务对其他 n 个任务进行检测的机制,并给出伪代码

10.5 对于嵌入式实时系统而言,频繁地创建、删除任务可能会有什么风险?请给出优化的解决方法

10.6 什么是函数的可重入问题?如何设计一个可重入的函数?

10.7 简述交叉编译工具链的工作原理,以及嵌入式软件的编译过程

10.8 简述模型驱动软件开发的基本过程